# Entwurf und Implementierung rekonfigurierbarer Controller für mechatronische Systeme

#### **Dissertation**

zur Erlangung des akademischen Grades

### Doktoringenieur

(Dr.-Ing.)

von Dipl.-Ing. Steffen Toscher

geb. am 8. Juli 1979 in Schwerin

genehmigt durch die Fakultät für Maschinenbau der Otto-von-Guericke-Universität

Magdeburg

Gutachter:

Prof. Dr.-Ing. Roland Kasper

Prof. Dr. rer. nat. Georg Rose

Promotionskolloquium am 15. Dezember 2008

### Vorwort

Die vorliegende Arbeit entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Institut für Mobile Systeme der Otto-von-Guericke-Universität Magdeburg. Ich möchte allen danken, die zum Gelingen beigetragen haben. Mein besonderer Dank gilt Prof. Dr.-Ing. Roland Kasper. Er gab mir die Gelegenheit, diese Arbeit am Lehrstuhl für Mechatronik durchzuführen und hat sie durch anregende Diskussionen und wichtige Ratschläge begleitet. Mein Dank gilt auch Dr.-Ing. Thomas Reinemann für Unterstützung, Ratschläge und Anregungen.

Prof. Dr. rer. nat. Georg Rose danke ich für wertvolle Hinweise und die Erstellung des Zweitgutachtens.

### Zusammenfassung

Heutige Standardimplementierungsplattformen für digitale Steuer- und Regelfunktionalitäten mechatronischer Systeme, wie Mikrocontroller und Signalprozessoren, basieren auf einer festen Hardwarearchitektur und der sequentiellen oder eingeschränkt parallelen Abarbeitung von Software. Moderne rekonfigurierbare Hardware stellt jedoch eine hohe Rechenleistung, harte Echtzeitfähigkeiten und eine allgemeine Hardwareprogrammierbarkeit zur Verfügung. Die grundlegende Strukturvariabilität rekonfigurierbarer Hardware ermöglicht darüber hinaus eine flexible Umsetzung digitaler Steuer- und Regelfunktionalitäten.

Die vorliegende Arbeit behandelt den Entwurf und die Implementierung rekonfigurierbarer Controller für mechatronische Systeme auf der Grundlage moderner rekonfigurierbarer FPGAs. Dabei wird die partielle Rekonfiguration als Möglichkeit genutzt, die Funktionalität der entworfenen Controller dynamisch an veränderte Hardwareanforderungen anzupassen. Die Arbeit stellt eine Entwurfsmethodik vor, die eine fachnahe Spezifikation und Umsetzung der partiellen Rekonfiguration ermöglicht. Der Entwurf strukturvariabler Funktionen wird weiterhin durch ein implizites und echtzeitfähiges verteiltes Rekonfigurationsmanagement unterstützt. Darüber hinaus werden Infrastrukturkomponenten und Funktionsgruppen entwickelt, die den Einsatz rekonfigurierbarer Hardware in mechatronischen Systemen unterstützen und vereinfachen. Die Anwendbarkeit und Leistungsfähigkeit der vorgestellten Methoden und Funktionsgruppen wird mit ausgewählten Beispielanwendungen nachgewiesen.

Inhaltsverzeichnis

## Inhaltsverzeichnis

| 1                   | Einleitung                             |                                                     |                                                                      | 1  |

|---------------------|----------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------|----|

|                     | 1.1                                    | Grundlagen rekonfigurierbarer Hardware              |                                                                      | 3  |

|                     | 1.2                                    | Field Programmable Gate Arrays                      |                                                                      |    |

|                     |                                        | 1.2.1                                               | Technologien und Hersteller                                          | 6  |

|                     |                                        | 1.2.2                                               | Architektur                                                          | 7  |

|                     |                                        | 1.2.3                                               | Dedizierte Funktionsblöcke                                           | 9  |

|                     |                                        | 1.2.4                                               | Programmierung                                                       | 10 |

|                     | 1.3                                    | Weiter                                              | re rekonfigurierbare Architekturen                                   | 10 |

|                     | 1.4                                    | Ziele o                                             | der Arbeit                                                           | 11 |

| 2                   | Star                                   | nd der T                                            | Гесhnik                                                              | 13 |

|                     | 2.1                                    | Entwu                                               | rfsmethoden                                                          | 13 |

| 2.2                 |                                        | Rekonfigurierbare Hardware in der Mechatronik       |                                                                      | 15 |

|                     | 2.3 Partielle Rekonfiguration von FPGA |                                                     | le Rekonfiguration von FPGAs                                         | 19 |

|                     |                                        | 2.3.1                                               | Hardwaregrundlagen                                                   | 20 |

|                     |                                        | 2.3.2                                               | Werkzeuge und Umsetzung                                              | 20 |

|                     |                                        | 2.3.3                                               | Anwendungen                                                          | 21 |

|                     |                                        | 2.3.4                                               | Weiterführende Ansätze                                               | 22 |

|                     | 2.4                                    | Bitseri                                             | ielle Signalverarbeitung                                             | 22 |

| 3                   | 3 Entwurfsmethodik                     |                                                     | ethodik                                                              | 24 |

|                     | 3.1                                    | Entwurfsgrundlagen                                  |                                                                      | 24 |

|                     |                                        | 3.1.1                                               | Vorgehensmodell                                                      | 25 |

|                     |                                        | 3.1.2                                               | Spezifikationswerkzeuge                                              | 26 |

|                     |                                        | 3.1.3                                               | Spezifikation der logischen Controllerstruktur mit Zustandsautomaten | 28 |

| 3.2 Partitionierung |                                        | Partiti                                             | onierung                                                             | 29 |

|                     |                                        | 3.2.1                                               | Partitionierung auf Funktionsebene                                   | 29 |

|                     |                                        | 3.2.2                                               | Partitionierung auf Hardwareebene                                    | 30 |

|                     | 3.3                                    | 3 Spezifikation rekonfigurierbarer Funktionalitäten |                                                                      | 32 |

|                     |                                        | 3.3.1                                               | Spezifikation rekonfigurierbarer Module                              | 32 |

|                     |                                        | 3.3.2                                               | Spezifikation von Hardwaretasks                                      | 34 |

|                     |                                        | 3.3.3                                               | Aktivierungsstrategien                                               | 36 |

Inhaltsverzeichnis

| 4 | Stru | ıktur u                                                         | nd Funktionsgruppen                                             | 38  |  |

|---|------|-----------------------------------------------------------------|-----------------------------------------------------------------|-----|--|

|   | 4.1  | Struktur rekonfigurierbarer Controller                          |                                                                 | 38  |  |

|   | 4.2  | Funkti                                                          | ionsgruppen                                                     | 41  |  |

|   |      | 4.2.1                                                           | Kommunikationssystem                                            | 42  |  |

|   |      | 4.2.2                                                           | Rekonfigurations- und Speichermanagement                        | 44  |  |

|   |      | 4.2.3                                                           | Zustandssicherung und Zustandswiederherstellung                 | 47  |  |

|   |      | 4.2.4                                                           | Controllerschnittstellen                                        | 49  |  |

|   | 4.3  | Spezif                                                          | fikationsframework                                              | 54  |  |

| 5 | Imp  | mplementierung                                                  |                                                                 |     |  |

|   | 5.1  | Zielha                                                          | ardware und Ressourcen                                          | 59  |  |

|   |      | 5.1.1                                                           | Rekonfigurierbare Controller auf Xilinx FPGAs                   | 59  |  |

|   |      | 5.1.2                                                           | Rekonfigurierbare Controller und bitserielle Signalverarbeitung | 64  |  |

|   |      | 5.1.3                                                           | Skalierung und Portierbarkeit                                   | 66  |  |

|   | 5.2  | Rekon                                                           | nfigurationslösung                                              | 67  |  |

|   |      | 5.2.1                                                           | Rekonfigurationsschnittstellen                                  | 68  |  |

|   |      | 5.2.2                                                           | Rekonfigurationsmechanismus                                     | 70  |  |

|   |      | 5.2.3                                                           | Rekonfigurationszeiten                                          | 73  |  |

|   | 5.3  | Imple                                                           | mentierungsschritte                                             | 74  |  |

|   |      | 5.3.1                                                           | Herstellerspezifische Implementierungsschritte                  | 74  |  |

|   |      | 5.3.2                                                           | Anbindung an das Spezifikationsframework                        | 78  |  |

|   | 5.4  | 5.4 Verifikation                                                |                                                                 | 78  |  |

|   |      | 5.4.1                                                           | Timingsimulationen                                              | 79  |  |

|   |      | 5.4.2                                                           | Messungen                                                       | 80  |  |

| 6 | Anv  | Anwendungen                                                     |                                                                 |     |  |

|   | 6.1  | Rekon                                                           | nfigurierbarer Antriebscontroller                               | 82  |  |

|   |      | 6.1.1                                                           | Spezifikation                                                   | 83  |  |

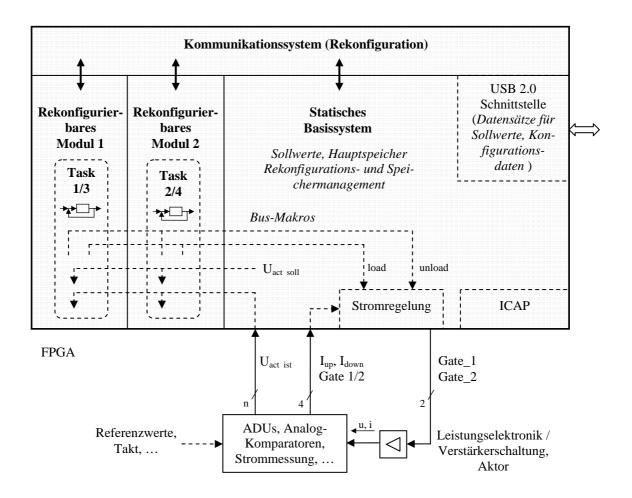

|   |      | 6.1.2                                                           | Struktur und Komponenten                                        | 84  |  |

|   |      | 6.1.3                                                           | Implementierung                                                 | 89  |  |

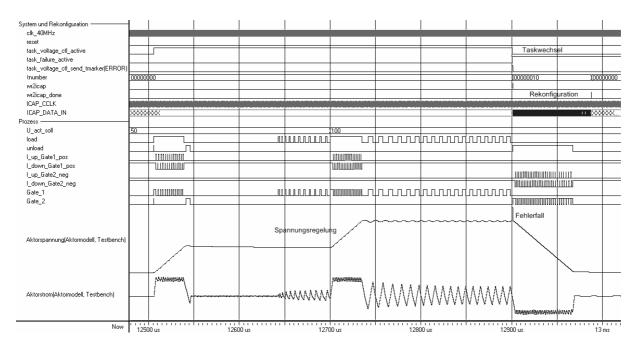

|   |      | 6.1.4                                                           | Verifikation                                                    | 91  |  |

|   | 6.2  | 6.2 Rekonfigurierbarer Controller für piezo-elektrische Aktoren |                                                                 | 94  |  |

|   |      | 6.2.1                                                           | Spezifikation                                                   | 95  |  |

|   |      | 6.2.2                                                           | Struktur und Komponenten                                        | 96  |  |

|   |      | 6.2.3                                                           | Implementierung                                                 | 100 |  |

| Inhal | tsverz | eıc | hnıs |

|-------|--------|-----|------|

|                                 |                      | 6.2.4 Verifikation                            | 102 |  |

|---------------------------------|----------------------|-----------------------------------------------|-----|--|

|                                 | 6.3                  | Rapid Prototyping und Steuergeräteentwicklung | 103 |  |

| 7                               | 7 Fazit und Ausblick |                                               | 106 |  |

| Bezeichnungen und Formelzeichen |                      |                                               |     |  |

| Literaturverzeichnis            |                      |                                               | 112 |  |

| Anhang                          |                      |                                               |     |  |

### 1 Einleitung

Die Anforderungen an moderne Elektronikbausteine und den daraus aufgebauten informationsverarbeitenden Komponenten mechatronischer Systeme haben in den letzten Jahren und Jahrzehnten stark zugenommen. Anwendungen, zum Beispiel im Fahrzeug, erfordern eine hohe Rechenleistung und harte Echtzeitfähigkeit bei gleichzeitig kostengünstigen Implementierungsmöglichkeiten. Heutige Standardimplementierungsplattformen für digitale Steuerund Regelfunktionalitäten mechatronischer Systeme, wie Mikrocontroller und Signalprozessoren, basieren auf einer festen Hardwarearchitektur und der sequentiellen oder eingeschränkt parallelen Abarbeitung von Software. Dieser Ansatz ermöglicht eine hohe Flexibilität in Bezug auf in Software implementierte Funktionen, da diese jederzeit an neue Anforderungen angepasst und verändert werden können. Aufgrund ihrer festen Hardwarearchitektur sind Mikrocontroller und Signalprozessoren jedoch nicht an sich verändernde Hardwareanforderungen anpassbar, zum Beispiel bei verändertem Rechen-, Kommunikations- oder I/O-Bedarf. Weiterhin wird die Rechenleistung und das Echtzeitverhalten von Mikrocontrollern, Universal- und Signalprozessoren durch die sequentielle Arbeitsweise limitiert, da nur eine begrenzte Anzahl von Verarbeitungselementen zur Verfügung steht. Bei mechatronischen Systemen, die hochdynamische Signalverarbeitung beinhalten, ist so die Anzahl der pro Tastperiode durchführbaren Operationen eingeschränkt.

Der Einsatz rekonfigurierbarer Hardware, insbesondere von *Field Programmable Gate Arrays* (FPGAs), für die Implementierung von Steuer- und Regelfunktionen in mechatronischer Systemen stellt einen Lösungsansatz für diese Probleme dar. Rekonfigurierbare Hardware ermöglicht eine parallele Informationsverarbeitung direkt in der Hardware und so eine sehr hohe Rechenleistung in Zusammenhang mit harter Echtzeitfähigkeit. Neben der hohen Rechenleistung stellen programmierbare Logikbausteine wie FPGAs sehr große Kommunikations- und I/O-Leistungen zur Verfügung. Eine weitere wesentliche Eigenschaft rekonfigurierbarer Hardware ist die Anpassung an veränderliche Hardwareanforderungen eines mechatronischen

Systems. Durch eine Rekonfiguration der Hardware kann so neuen Anforderungen an Funktionalität, Rechenleistung und Schnittstellen im Entwicklungsprozess oder Produktlebenszyklus entsprochen werden. Eine solche Anpassung erfolgt im Normalfall durch eine Umprogrammierung der kompletten Hardware eines Bausteins außerhalb des regulären Betriebs. Während der Laufzeit eines auf diese Weise implementierten Controllers sind alle benötigten Hardwarekomponenten nebeneinander auf dem Baustein realisiert, auch wenn diese nie gleichzeitig benutzt werden. Eine wesentlich größere Flexibilität und eine bessere Ausnutzung der Hardwareressourcen bieten auf modernen FPGAs implementierte partiell und dynamisch rekonfigurierbare Controller. Sie ermöglichen eine dynamische Anpassung von Rechen- und Kommunikationsleistung, Steuerungs- und Regelungsfunktionen sowie Schnittstellen an den jeweiligen Betriebszustand während der Laufzeit des Controllers. Für die Echtzeitfähigkeit eines so implementierten Controllers ist entscheidend, dass die partiellen Konfigurationsänderungen der Hardware unter Einhaltung von Echtzeitbedingungen ablaufen.

Der Entwurf und die Implementierung solcher partiell und dynamisch rekonfigurierbaren Controller für mechatronische Systeme ist Gegenstand der vorliegenden Arbeit. Sie gliedert sich wie folgt:

Kapitel 1 gibt neben der allgemeinen Einleitung einen Überblick über rekonfigurierbare Hardware und geht speziell auf FPGAs ein. Kapitel 2 stellt aktuelle Entwurfsverfahren für Steuerungs- und Regelungseinrichtungen im Bereich der Mechatronik vor und erläutert den Einsatz rekonfigurierbarer Hardware in der Mechatronik. Ein weiterer Schwerpunkt sind Grundlagen, Werkzeuge und Anwendungen der partiellen Rekonfiguration moderner FPGAs. Die der vorliegenden Arbeit zugrunde liegende neue Entwurfsmethodik für rekonfigurierbare Controller in mechatronischen Systemen wird in Kapitel 3 beschrieben. Dabei wird auf Entwurfsverfahren, Partitionierung und ein verteiltes echtzeitfähiges Rekonfigurationsmanagement eingegangen. In Kapitel 4 werden die entwickelte Struktur und Funktionsgruppen für rekonfigurierbare Controller in der Mechatronik dargestellt. Ausgehend von der Struktur rekonfigurierbarer Controller beschreibt Kapitel 5 die Implementierung auf der Zielhardware und geht insbesondere auf die entwickelten echtzeitfähigen Rekonfigurationsmechanismen ein. Schließlich werden in Kapitel 6 Anwendungen rekonfigurierbarer Controller in mechatronischen Systemen vorgestellt, die auf den Ergebnissen der Arbeit basierend entworfen und implementiert wurden. Schwerpunkte sind ein rekonfigurierbarer Antriebscontroller für DC-Antriebe und ein rekonfigurierbarer Controller für die Ansteuerung piezo-elektrischer Aktoren.

### 1.1 Grundlagen rekonfigurierbarer Hardware

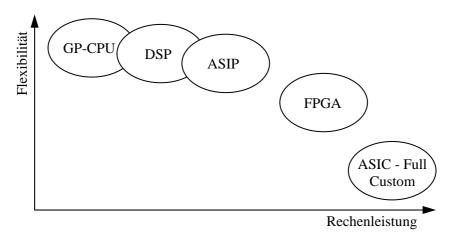

Die Realisierung komplexer Algorithmen in der Digitaltechnik kann grundsätzlich auf vielen verschiedenen Architekturen erfolgen. Wesentliche Auswahlkriterien hierbei sind die für die Anwendung benötigte Rechenleistung und die zugrunde liegende Flexibilität der Zielarchitektur. Abbildung 1 gibt qualitativ eine Übersicht über die subjektive Flexibilität verschiedener Architekturen gegenüber ihrer Rechenleistung.

Abbildung 1: Vergleich verschiedener Architekturen nach Flexibilität und Rechenleistung

Größtmögliche Flexibilität bieten Universalprozessoren (General Purpose CPUs, GP-CPUs). Sie zeichnen sich durch eine feste Hardwarearchitektur aus und basieren auf der sequentiellen oder eingeschränkt parallelen Abarbeitung von Instruktionen. Die zu implementierende Funktionalität wird durch die Instruktionen in Software abgebildet und durch die Ausführung der Instruktionen auf der universellen und festen Prozessorhardware umgesetzt [1]. Die softwareseitige Programmierung ermöglicht es, Universalprozessoren für verschiedenste Anwendungsgebiete flexibel einzusetzen. Eine Änderung der implementierten Funktionalität erfolgt durch eine Anpassung der Software, die Hardware ist nicht veränderlich. Allerdings ist die Rechenleistung von Universalprozessoren durch die feste Hardware und die sequentielle Programmausführung begrenzt. Weitere durch Software programmierbare Architekturen sind domänenspezifische Prozessoren wie digitale Signalprozessoren (DSPs) und Prozessoren mit anwendungsspezifischem Instruktionssatz (Application Specific Instruction Set Processors, ASIPs). Diese Architekturen basieren ebenfalls auf einer festen Hardwarearchitektur und der sequentiellen sowie eingeschränkt parallelen Abarbeitung von Software, sind jedoch auf bestimmte Algorithmenklassen und Anwendungen spezialisiert [2]. Die Spezialisierung der Hardware führt zu einer erhöhten Rechenleistung und verbesserten Ressourcennutzung, aber auch einer verringerten Flexibilität gegenüber Universalprozessoren.

Den flexiblen durch Software programmierbaren Architekturen entgegengesetzt sind kundenund anwendungsspezifische integrierte Schaltungen (*Application Specific Integrated Circuits*,

ASICs), die bis in die Transistorebene auf maximale Rechenleistung und Datendurchsatz optimiert sind. Der Begriff ASIC beschreibt eine große Gruppe von Bausteinen, die in ihrer

Hardwarestruktur für eine bestimmte Anwendung optimiert sind [3]. Diese Architekturen

implementieren sämtliche Funktionalität direkt in Hardware und können nach der Fertigung

des Bausteins nicht mehr geändert werden. Die Flexibilität von ASICs ist so stark eingeschränkt. Eine gewisse Anpassungsfähigkeit kann jedoch durch im Baustein eingebettete Prozessoren erreicht werden (*System on Chip*, SoCs). Die am weitesten spezialisierte und vollkundenspezifische Form von ASICs sind Full Custom Makros.

Einen Kompromiss zwischen der Flexibilität softwareprogrammierbarer Lösungen und der hohen Rechenleistung anwendungsspezifischer Schaltungen bieten rekonfigurierbare Architekturen. Ihre Rechenleistung kommt in die Nähe anwendungsspezifischer Bausteine, jedoch kann die implementierte Funktionalität auch nach der Fertigstellung der Komponente an die jeweilige Anwendung angepasst (rekonfiguriert) werden. Die Anpassung der Hardwarestruktur an neue Anforderungen stellt den wesentlichen Aspekt rekonfigurierbarer Hardware dar. Der Begriff Rekonfiguration kann nach [4] als Prozess der Anpassung und Veränderung der Hardwarestruktur einer Komponente beschrieben werden. Eine weitere Differenzierung ergibt sich aus der Art der Rekonfiguration einer Hardwarekomponente. Erfolgt eine Anpassung und Veränderung der Hardwarestrukturen lediglich außerhalb des Betriebs und der Laufzeit einer Hardwarekomponente, wird dies als statische Rekonfiguration oder Konfiguration bezeichnet. Die dynamische Rekonfiguration einer Hardwarekomponente wird dagegen durch die Anpassung und Veränderung der Hardwarestrukturen während des laufenden Betriebs charakterisiert. Eine weitergehende Differenzierung der dynamischen Rekonfiguration ergibt sich aus der Art der Hardwareanpassung [5]. Kann im laufenden Betrieb nur die gesamte Hardwarestruktur verändert werden, so bedingt dies in einem System mit nur einer Konfigurationsebene (Einzelkontextsystem) den zeitkritischen Austausch sämtlicher Konfigurationsdaten. Durch die Einführung mehrerer Konfigurationsebenen (Multikontextsystem) können verschiedene Hardwarekonfigurationen gleichzeitig vorgehalten werden, zwischen denen zur Laufzeit gewechselt werden kann. Problematisch sind der wesentlich höhere Speicherbedarf und die schlechte Ressourcennutzung gegenüber Systemen mit nur einer Konfigurationsebene. Einen deutlich flexibleren Ansatz verfolgt die partielle Rekonfiguration von Systemen mit nur einer Konfigurationsebene: während ein Teil der Hardware in Betrieb bleibt, wird ein anderer Teil umkonfiguriert. Bedingung ist hierbei, dass Teile der Konfigurationsebene einzeln angespro-

chen werden können. Die partielle Rekonfiguration erhöht auf diese Weise die Flexibilität und Ressourceneffizienz rekonfigurierbarer Architekturen. Zusätzlich können auf Grundlage der partiellen Rekonfiguration Prinzipien und Methoden der Softwaretechnik auf rekonfigurierbare Hardware übertragen werden. Systeme, die von einer partiellen Rekonfiguration profitieren und diese einsetzen, finden sich bereits im Bereich der Kommunikationstechnik und Videoverarbeitung [4]. Hier unterstützt die partielle Rekonfiguration den dynamischen Zugriff auf Funktionalitäten zur Laufzeit des Systems ohne Erhöhung des Ressourcenbedarfs. Vergleichbare Ansätze für die Steuerung und Regelung mechatronischer Systeme existieren jedoch kaum.

Ein weiteres wesentliches Unterscheidungsmerkmal rekonfigurierbarer Architekturen ist ihre *Granularität* [4]. Der Granularitätsgrad ergibt sich aus den Konfigurationsmöglichkeiten einer Komponente: die Funktionalität feingranularer Architekturen kann bis zur Bitebene modifiziert werden, die Funktionalität grobgranularer Architekturen jedoch nur in Blöcken mit einer bestimmten Wortbreite wie 8,16 oder 32 Bit. Eine kurze Beschreibung grobgranularer Architekturen erfolgt in Abschnitt 1.3. Die Gruppe der feingranularen Architekturen wird hauptsächlich von programmierbaren Logikbausteinen (*Programmable Logic Devices*, PLDs), insbesondere *Complex Programmable Logic Devices* (CPLDs) und *Field Programmable Gate Arrays* (FPGAs), gebildet.

### 1.2 Field Programmable Gate Arrays

FPGAs wurden im Jahr 1985 von der US-amerikanischen Firma Xilinx auf den Markt gebracht und stellen heute die bedeutendste Gruppe rekonfigurierbarer Hardware dar. Während die frühen FPGAs vor allem für die Realisierung dichter Verbindungen (Glue Logic) zwischen digitalen Bausteinen eingesetzt wurden, sind heutige FPGAs wesentlich leistungsfähiger und können zur Implementierung kompletter digitaler Systeme verwendet werden. Wichtige Einsatzgebiete sind digitale Signalverarbeitung und eingebettete Systeme. Die Bezeichnung *Field Programmable Gate Array* bezieht sich auf die grundlegende Eigenschaft von FPGAs, nach der Herstellung und damit "im Feld" oder Einsatzgebiet programmierbar zu sein. Weiterführende Informationen zu Grundlagen und Einsatzgebieten von FPGAs sind in [6], [7] und [8] zu finden.

### 1.2.1 Technologien und Hersteller

Zur Herstellung von FPGAs werden je nach Produzent und gewünschten Eigenschaften unterschiedliche Technologien eingesetzt. Moderne FPGAs lassen sich so in SRAM-, Flash-EEPROM- und Antifuse-basierte Bausteine einteilen. Die nur einmal programmierbaren Antifuse-FPGAs sind für den flexiblen Einsatz als rekonfigurierbare Hardwarekomponente ungeeignet. SRAM und Flash-basierte FPGAs können dagegen mehrfach programmiert werden und sind rekonfigurierbare Hardwarekomponenten. Die große Mehrheit der heute eingesetzten FPGAs nutzt die SRAM-Technologie, da diese ein unbegrenztes und flexibles Programmieren der Hardware erlaubt. Allerdings ist SRAM im Gegensatz zu Flash-EEPROM eine flüchtige Speichertechnologie, so dass SRAM-basierte FPGAs bei jedem Systemstart neu konfiguriert werden müssen. Hierfür wird meist ein externer nicht flüchtiger Speicher eingesetzt. Aufgrund der großen Verbreitung und Marktdominanz SRAM-basierter Architekturen bezieht sich der Begriff FPGA in der vorliegenden Arbeit vorwiegend auf SRAM-basierte FPGAs.

Marktführender Hersteller von FPGAs ist die US-amerikanische Firma Xilinx. Sie stellt SRAM-basierte FPGAs sowohl für den Hochleistungsbereich als auch für kostensensitive Anwendungen her. Der Hochleistungsbereich wird von Xilinx Virtex FPGAs abgedeckt, die eine hohe Logikdichte mit integrierten dedizierten Funktionsblöcken kombinieren. Die aktuellen Vertreter dieser Familie wie die Virtex-4 und Virtex-5 FPGAs verfügen je nach Ausstattung unter anderem über eingebettete Multiplizierer, DSP-Blöcke und Prozessoren [9]. Gegenwärtige Vertreter der kostengünstigeren und kleineren Xilinx Spartan FPGAs sind die Spartan-3 Bausteine, von denen auch eine nicht flüchtige Flash-basierte Variante erhältlich ist [10]. Ein weiterer führender Hersteller von FPGAs ist die Firma Altera, die ähnlich wie Xilinx Hochleistungsbausteine und kostengünstige einfachere FPGAs auf SRAM-Basis anbietet. Aktuelle Hochleistungsbausteine sind die Stratix II und III FPGAs [11]. Die kostengünstigen Bausteine werden als Cyclone vermarktet. Weitere wichtige Hersteller von FPGAs sind unter anderem Lattice und Actel. Lattice stellt sowohl FPGAs auf Basis von SRAM (LatticeSC, LatticeECP2) als auch auf einer kombinierten Basis von Flash und SRAM (LatticeXP2 [12]) her. Actel produziert vor allem Flash-basierte FPGAs. Eine Besonderheit stellen die Actel Fusion Mixed-Signal FPGAs dar, die über einen integrierten Analog/Digital-Wandler sowie weitere analoge Funktionen verfügen [13].

#### 1.2.2 Architektur

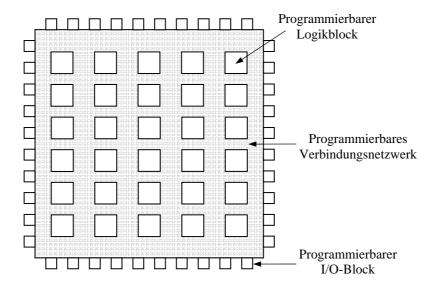

Die grundlegende Architektur eines FPGAs entspricht einem regelmäßigen zweidimensionalen Feld von programmierbaren Logikblöcken, das mit einem programmierbaren Verbindungsnetzwerk versehen ist und über programmierbare I/O-Blöcke mit der Außenwelt kommuniziert. Abbildung 2 zeigt den prinzipiellen Aufbau eines FPGAs aus diesen drei Grundelementen. Die dargestellte Architektur entspricht einem symmetrischen Array und wird auch als *Island-Style-*Topologie bezeichnet, da die Logikblöcke wie Inseln im Verbindungsnetzwerk integriert sind. Vor allem FPGAs der marktführenden Firmen Xilinx und Altera nutzen diese Struktur. Altera FPGAs sind dabei auch hierarchisch strukturiert, indem Logikblöcke zu übergeordneten Gruppen zusammengefasst werden. Weitere mögliche FPGA-Strukturen umfassen unter anderem reihenbasierte Lösungen [4]. Die folgenden Absätze geben eine kurze Beschreibung der drei genannten Grundelemente von FPGAs.

Abbildung 2: Grundlegende Architektur eines FPGAs [8]

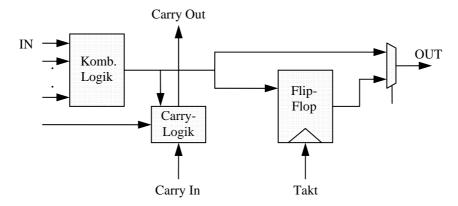

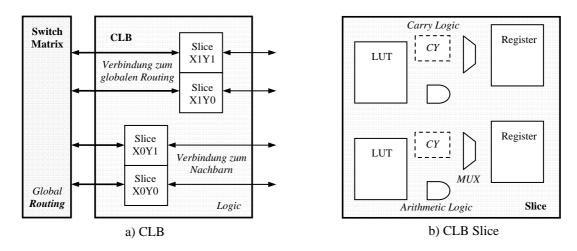

Die Basis für die Implementierung von logischen Funktionen auf einem FPGA bilden programmierbare Logikblöcke. Sie bestehen heute herstellerübergreifend meist aus programmierbarer kombinatorischer Logik, Flipflops und schneller Übertragslogik (Carry Logic). Abbildung 3 zeigt den prinzipiellen Aufbau eines solchen programmierbaren Logikblocks. Die in heutigen FPGAs eingesetzten Logikblöcke sind oft sehr flexibel konfigurierbar. So können die Flipflops takt- oder zustandsgesteuert (Latch) eingesetzt und mit synchronen und asynchronen Setz- und Rücksetzsignalen beaufschlagt werden. Weiterhin erfüllt die Übertragslogik häufig zusätzliche Funktionen, wie weitergehende Unterstützung bei Multiplikation und Addition. Die programmierbare kombinatorische Logik innerhalb eines Logikblocks wird

allgemein mit Look-Up-Tables (LUTs) realisiert. Dabei handelt es sich um programmierbare SRAM-Speicherzellen, die beliebige logische Funktionen abbilden. Für einen LUT mit vier Eingängen, wie er in modernen FPGAs aus Flächengründen meist eingesetzt wird, wird beispielsweise ein 16x1 Bit Speicher benötigt. Eine Alternative zu LUTs stellen Kombinationen von Multiplexern und Logikgattern dar. In vielen modernen FPGAs werden die einzelnen programmierbaren Logikblöcke in Gruppen zusammengefasst, um so größere Funktionen effektiver implementieren zu können. Diese Bereiche bestehen in einem Xilinx Virtex-4 FPGA aus acht Blöcken mit vier Eingängen und in einem Altera Stratix-II FPGA aus 24 Blöcken mit drei Eingängen und 16 Blöcken mit vier Eingängen ([9] [11]). Hier ist deutlich der hierarchische Ansatz in Altera FPGAs zu erkennen.

Abbildung 3: Prinzipielle Struktur eines programmierbaren Logikblocks [8]

Die programmierbaren Verbindungsnetzwerke in FPGAs sind für die lokale Verbindung von Logikblöcken innerhalb der übergeordneten Gruppen und die globale Verbindung der Gruppen und Blöcke verantwortlich. Für die komplexeren globalen Verbindungen haben sich insbesondere zwei grundlegende Routing-Architekturen durchgesetzt: die oben bereits genannte Island-Style-Architektur und die Long-Line-Architektur. Die Island-Style-Architektur basiert auf Schaltmatritzen (Switch Boxes), die einzelne horizontale und vertikale Segmente der globalen Verbindungsleitungen flexibel verbinden. Logikblöcke bzw. Gruppen von Blöcken sind über Verbindungsstellen (Connection Boxes) an die globalen Verbindungsleitungen angekoppelt. Die Long-Line-Architektur basiert dagegen auf Leitungen, die die gesamte Länge oder Breite des FPGAs einschließen. Auf diese Weise können Gruppen und Logikblöcke über die Zusammenschaltung von zwei oder mehr Leitungen verbunden werden. Die beiden Routing-Architekturen werden in modernen FPGAs oft kombiniert eingesetzt. Eine detaillierte Darstellung und Klassifizierung der verschiedenen Verbindungsnetzwerke findet sich in [8].

Die Verbindung der inneren Strukturen mit den Anschlusskontakten eines FPGAs wird über programmierbare I/O-Blöcke realisiert. Grundlegende Bestandteile der I/O-Blöcke sind Input-Buffer für die Eingänge und Tri-State-Buffer für die Ausgänge. Zusätzlich können die verschiedenen Signale eines I/O-Blocks, wie das Freigabesignal für den Tri-State sowie Eingangs- und Ausgangssignale, je nach Programmierung über Register geführt werden. Diese elementare Struktur der I/O-Blöcke ist bei den meisten Architekturen und Herstellern sehr ähnlich. Die I/O-Blöcke heutiger FPGAs verfügen darüber hinaus über eine Vielzahl zusätzlicher Funktionen, die den Einsatz von FPGAs in vielen Anwendungen erleichtern. So können verschiedenste I/O-Standards eingestellt und Verzögerungszeiten für Eingänge vorgegeben werden.

#### 1.2.3 Dedizierte Funktionsblöcke

Moderne FPGAs enthalten neben den oben beschriebenen grundlegenden Architekturkomponenten oft weitere spezialisierte Funktionsblöcke, die die Funktionalität für verschiedene Anwendungsgebiete erweitern. Dies führt zu deutlich heterogeneren Strukturen heutiger FPGA-Architekturen. In fast allen heute auf dem Markt befindlichen FPGAs sind eingebettete RAM-Blöcke vorhanden, die eine effiziente Implementierung von Speicherkomponenten ermöglichen ohne auf die Flipflops und LUTs der Grundarchitektur zurückzugreifen. Die Größe und Anzahl der dedizierten Speicherblöcke ist je nach Architektur, Hersteller und Produktfamilie unterschiedlich. Die größeren heute erhältlichen FPGAs enthalten in der Summe der verteilten Blöcke bis zu 1 MB dedizierten Speicher, der über die große Zahl der Ports sehr flexibel ansprechbar ist. Eine weitere ergänzende Komponente moderner FPGAs sind eingebettete Blöcke zur direkten und effizienten Umsetzung arithmetischer Operationen. Häufig werden einzelne dedizierte Multiplizierer oder konfigurierbare DSP-Blöcke eingesetzt. Die DSP-Blöcke können unter anderem Addition, Subtraktion, Multiplikation implementieren und so die Realisierung von Signalverarbeitungsalgorithmen wesentlich effizienter ermöglichen.

Eine besondere Stellung nehmen moderne FPGAs mit eingebetteten Mikroprozessoren ein. Diese erweitern die hohe Rechenleistung und hardwarebezogene Flexibilität eines FPGAs um die Flexibilität softwareprogrammierbarer Systeme. So ist es möglich, ganze eingebettete Systeme auf nur einem FPGA zu implementieren. Beispiele sind die älteren ARM-basierten Altera Excalibur FPGAs und die neueren PowerPC-basierten Xilinx Virtex-II Pro, Virtex-4 FX und Virtex-5 FX FPGAs [14]. An dieser Stelle sollen außerdem die so genannten Softcore-Mikroprozessoren erwähnt werden. Im Gegensatz zu den oben genannten Prozessoren sind sie nicht als dedizierte Funktionsblöcke fest auf den FPGAs vorhanden, sondern werden flexibel

mit den grundlegenden Ressourcen eines FPGAs implementiert. Beispiele für diese Klasse von eingebetteten Mikroprozessoren sind der MicroBlaze von Xilinx [15], der NIOS II von Altera [16] und der LatticeMICO32 [17].

### 1.2.4 Programmierung

Die Programmierung SRAM-basierter FPGAs beschreibt die Art und Weise in der Konfigurationsdaten (Bitstream) auf den Baustein geladen werden und die grundlegenden SRAM-Zellen konfigurieren. Die Konfigurationsdaten werden vorher von den Implementierungswerkzeugen des FPGA-Herstellers aus einer vom Anwender erstellten Spezifikation erzeugt. Für die initiale Konfiguration werden die erforderlichen Daten meist von einer übergeordneten Ebene wie PC, Mikrocontroller oder externem Programmierspeicher (PROM) an eine der Programmierschnittstellen des FPGAs geschickt und konfigurieren den gesamten Baustein. Die Programmierschnittstellen basieren dabei auf serieller oder 8 bzw. 32 Bit Datenübertragung und laufen mit Geschwindigkeiten von 1-100 MHz. Übliche Konfigurationszeiten liegen bei einigen hundert Mikrosekunden bis Sekunden. Die bekannteste serielle Schnittstelle ist das Boundary Scan Interface (Joint Test Action Group, JTAG). Die partielle Rekonfiguration von FPGAs, also die Umprogrammierung von Hardwarebereichen im laufenden Betrieb, setzt insbesondere eine Möglichkeit zur getrennten Konfiguration einzelner Bereiche des FPGAs voraus. Eine der wenigen FPGA-Architekturen, die über eine entsprechende Granularität der Konfiguration verfügen, sind Xilinx FPGAs. Abschnitt 2.3 dieser Arbeit geht näher auf die partielle Rekonfiguration von FPGAs ein.

### 1.3 Weitere rekonfigurierbare Architekturen

Die Gruppe programmierbarer Logikbausteine umfasst neben FPGAs weiterhin die *Complex Programmable Logic Devices* (CPLDs). CPLDs bestehen aus größeren Blöcken von programmierbaren UND- und ODER-Feldern (*Programmable Logic Arrays*, PALs) und haben einen komplexeren Aufbau als FPGAs. Sie erreichen jedoch nicht deren Leistungsfähigkeit und werden vor allem als Verbindungslogik eingesetzt. Eine Besonderheit stellt der Altera MAX II CPLD dar: er ist als Multikontextsystem realisiert und kann so im laufenden Betrieb zwischen verschiedenen Hardwarekonfigurationen wechseln [18]. Als mit programmierbaren Logikbausteinen verwandte Architekturen sind weiterhin Mikrocontroller mit eingebetteten FPGAs zu erwähnen. Hier wird ein Mikroprozessor mit festen Peripheriekomponenten um ein kleineres meist SRAM-basiertes FPGA erweitert. Als Beispiel sei die Atmel FPSLIC Archi-

tektur genannt, die ebenfalls die dynamische Rekonfiguration des eingebetteten FPGAs unterstützt ([19] [20]).

Eine konsequente Weiterentwicklung stark heterogener FPGAs oder Mikroprozessoren mit eingebetteten FPGAs sind die Coarse-Grained Reconfigurable Devices (CGRDs). Viele CGRDs bestehen aus einer Anordnung von grobgranularen programmierbaren Funktionsblöcken und einem programmierbaren Verbindungsnetzwerk. Die Funktionsblöcke sind meist arithmetisch-logische Einheiten (ALUs) für die Ausführung von Additions-, Subtraktionsund Multiplikationsoperationen. Die Wortbreite der Funktionsblöcke ist im Gegensatz zu feingranularen Architekturen fest und beträgt meist 8, 16 oder 32 Bit. Für spezifische Anwendungen bieten CGRDs daher eine bessere Flächen- und Energieeffizienz als feingranulare Strukturen, jedoch auf Kosten der Flexibilität. Als Beispiel sei hier die PACT XPP-III Architektur erwähnt, die auf dem genannten Prinzip von grobgranularen Funktionsblöcken und konfigurierbaren Verbindungsnetzwerken basiert [21]. Ein weiteres Beispiel grobgranularer Architekturen sind die software-konfigurierbaren Prozessoren der Firma Stretch, die eine Weiterentwicklung von Mikroprozessoren mit eingebettetem FPGA darstellen [22]. Besonderes Merkmal dieser Architektur ist eine konfigurierbare Erweiterung des Instruktionssatzes in Hardware. Weitergehende Informationen zu grobgranularen Architekturen sind in [4], [8] und [23] zu finden.

#### 1.4 Ziele der Arbeit

Das Ziel der vorliegenden Arbeit ist es, Methoden und Vorgehensweisen für den Entwurf und die Implementierung flexibler Controller in mechatronischen Systemen auf der Basis moderner rekonfigurierbarer Hardware zu entwickeln. Dabei wird insbesondere die partielle Rekonfiguration als Möglichkeit genutzt, die Funktionalität der entworfenen Controller dynamisch an veränderte Hardwareanforderungen anzupassen. Ein Teilziel der Arbeit ist daher die Entwicklung einer Entwurfsmethodik, die sich in bestehende Entwurfskonzepte mechatronischer Systeme integriert und den Entwurf strukturvariabler Funktionalitäten durch ein implizites Rekonfigurationsmanagement unterstützt. Weiterhin werden essentielle Funktionsgruppen rekonfigurierbarer Controller entwickelt und in ein durchgängiges Spezifikationsframework eingebunden. Ziel ist es, mit den entwickelten Funktionsgruppen eine Infrastruktur zu schaffen, die den Einsatz partiell rekonfigurierbarer Hardware für mechatronische Systeme unterstützt und vereinfacht. Von besonderer Bedeutung ist dabei die Entwicklung eines hardwarenahen und echtzeitfähigen Rekonfigurationsmechanismus. Als Zielhardware für die Control-

ler und deren Funktionsgruppen werden FPGAs eingesetzt. Die Implementierung aller Funktionalitäten erfolgt direkt in Hardware und gewährleistet die harte Echtzeitfähigkeit der Controller. Abschließendes Ziel der Arbeit ist es, die Anwendbarkeit und Leistungsfähigkeit der entwickelten Methoden und Funktionsgruppen mit ausgewählten Beispielimplementierungen aus dem Bereich der Mechatronik aufzuzeigen.

### 2 Stand der Technik

Dieses Kapitel der Arbeit stellt den Stand der Forschung und Technik im Bereich rekonfigurierbarer Hardware und deren Einsatz in der Mechatronik vor. Dabei wird zuerst auf gebräuchliche Entwurfsmethoden für Steuer- und Regelfunktionalitäten in mechatronischen Systemen eingegangen, da diese grundlegend für die zu entwickelnden rekonfigurierbaren Controller sind. Es folgt eine Übersicht über den Einsatz rekonfigurierbarer Hardware in verschiedenen Anwendungsgebieten der Mechatronik mit entsprechenden Beispielen. Der dritte Abschnitt dieses Kapitels beschreibt Hintergründe und Möglichkeiten der partiellen Rekonfiguration heutiger FPGAs. Das Kapitel schließt mit den Grundlagen bitserieller Signalverarbeitung, die für die Implementierung rekonfigurierbarer Funktionalitäten in der vorliegenden Arbeit eingesetzt wird.

#### 2.1 Entwurfsmethoden

Heutige mechatronische Systeme, z.B. im Fahrzeug, sind durch einen hohen Anteil von Elektronik und Software geprägt. Der Entwurf und die Funktionsentwicklung der darin implementierten Steuer- und Regelfunktionalitäten erfordern Methoden, die sich in übergeordnete Entwicklungsprozesse einordnen und so eine durchgängige System- und Produktentwicklung unterstützen.

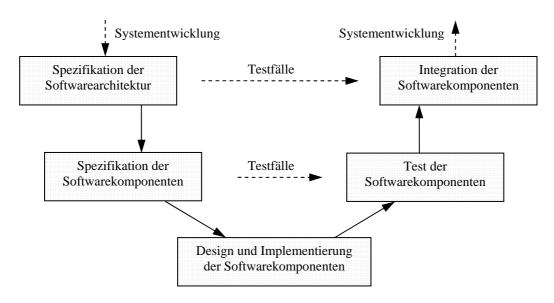

Von besonderer Bedeutung für die Entwicklung mechatronischer Systeme und insbesondere den Entwurf von Steuer- und Regelfunktionalitäten ist das ursprünglich aus der Softwareentwicklung stammende V-Modell [24]. Dieses Vorgehensmodell trennt die Systementwicklung in eine absteigende und eine aufsteigende Entwicklungsphase. Die erste Phase beginnt mit der Definition der Benutzeranforderungen und geht über die Systemspezifikation und den eigentlichen Systementwurf bis zur Systeminplementierung. Die zweite Entwicklungsphase führt von der Systemintegration, also dem Zusammenführen entwickelter Komponenten, über Systemintegration, also dem Zusammenführen entwickelter Komponenten, über Systeminerung von der Systemintegration, also dem Zusammenführen entwickelter Komponenten, über Systeminerung von der Systemine

temtests bis zur Abnahme des Gesamtsystems. Eine gedankliche Zusammensetzung beider Entwicklungsphasen führt zu dem namensgebenden Gesamtmodell des Vorgehens. Die Systementwicklung nach dem V-Modell findet sich in einer angepassten Form auch in der VDI-Richtlinie 2206 "Entwicklungsmethodik für mechatronische Systeme" [25].

Als exemplarische Anwendung des V-Modells für den Entwurf von Steuer- und Regelfunktionalitäten mechatronischer Systeme kann die Systementwicklung eingebetteter Systeme (Steuergeräte) im Kraftfahrzeug betrachtet werden. Ein beispielhaftes V-Modell für diesen Anwendungsfall wird in [26] vorgestellt und ausführlich beschrieben. Der dort dargestellte Systementwicklungsprozess lässt sich grob in einen übergeordneten Teil der Systementwicklung und einen untergeordneten Teil der Komponentenentwicklung aufteilen. Der Entwurf von Steuer- und Regelfunktionalitäten erfolgt dabei vor allem im Kontext der Softwareentwicklung, die einen Zweig der Komponentenentwicklung bildet. Abbildung 4 zeigt den auf die Softwareentwicklung bezogenen Teil des zugrunde liegenden V-Modells.

Abbildung 4: Ausschnitt aus einem V-Modell zur Systementwicklung eingebetteter Systeme im Kraftfahrzeug [26]

Besondere Bedeutung im Entwicklungsprozess kommt den Spezifikationsmitteln für Steuerund Regelfunktionalitäten zu. Dies bezieht sich in der Entwicklung mechatronischer Systeme vor allem auf die Spezifikation der Softwarekomponenten. Übliche Spezifikationsmittel sind hier überwiegend grafische Methoden wie Blockdiagramme für den Datenfluss und flache oder hierarchische Zustandsautomaten für den Kontrollfluss. Weiterhin werden Entscheidungstabellen und Programmiersprachen wie C oder C++ direkt eingesetzt. Für eine ausführliche Beschreibung der genannten Spezifikationsmittel und deren Einordnung in den Entwicklungsprozess sei auf [27] verwiesen. Werkzeuge für die Funktionsentwicklung, die diese Spe-

zifikationsmittel einsetzen, sind unter anderem Matlab/Simulink der Firma The Mathworks, LabVIEW von National Instruments und ASCET der ETAS GmbH.

Die Entwicklung von Funktionen und Komponenten, die zur Implementierung in rekonfigurierbarer Hardware wie FPGAs bestimmt sind, kann analog zu der Entwicklung von Softwarekomponenten in das V-Modell eingegliedert werden. Für den Entwurf dieser Funktionalitäten werden grundlegend ähnliche Spezifikationsmethoden wie in der Softwareentwicklung angewandt. Da die entsprechenden Werkzeuge allerdings aus der Digitalelektronik und Hardwareentwicklung stammen, sind sie meist nur eingeschränkt in mechatronische Entwicklungsprozesse integrierbar. Dies trifft speziell auf die eingesetzten Hardwarebeschreibungssprachen wie VHDL und Verilog zu [28].

Eine systemübergreifende Alternative zu den genannten Spezifikationsmitteln bietet die *Unified Modeling Language* (UML). Die standardisierte Modellierungssprache stammt aus der Softwareentwicklung betrieblicher Anwendungssysteme und verfügt über komplexe grafische Beschreibungsformen für die Modellierung von Prozessen, Software und Systemen. Der Einsatz von UML für den Entwurf mechatronischer Systeme und deren Steuer- und Regelfunktionalitäten ist jedoch aufgrund der primären Ausrichtung auf betriebliche Softwaresysteme sehr komplex und nur eingeschränkt möglich. Entsprechende Ansätze, Methoden und Werkzeuge werden unter anderem in [29] vorgestellt. Weitere Einsatzmöglichkeiten der UML in verwandten Domänen sind der Entwurf eingebetteter Systeme und Echtzeitsysteme und das Hardware/Software-Codesign für rekonfigurierbare Architekturen ([30] [31]). Auch hier sind UML-basierte Entwurfsmethoden sehr komplex und nur eingeschränkt in bestehende Verfahren integrierbar. Aus den genannten Gründen wird die UML in der vorliegenden Arbeit nicht als Spezifikationsmittel verwendet.

### 2.2 Rekonfigurierbare Hardware in der Mechatronik

Die Standardimplementierungsplattform für digitale Steuer- und Regelfunktionalitäten in mechatronischen Systemen stellen heute Mikrocontroller dar. Rekonfigurierbare Hardware wird dagegen selten zur Umsetzung von Steuer- und Regelfunktionalitäten genutzt und dient in vielen Systemen vorwiegend zur Realisierung peripherer und zeitkritischer I/O-Funktionen. Moderne FPGAs bieten jedoch flexible Hardwareplattformen mit hoher Rechenleistung und harten Echtzeitfähigkeiten, die in vielen mechatronischen Systemen vorteilhaft eingesetzt werden können. Beispiele für mechatronische Systeme mit harten Echtzeitanforderungen sind unter anderem Kfz-Steuergeräte und sicherheitskritische Steuersysteme in der Luftfahrt. Steu-

ergeräte für die Ansteuerung von Verbrennungsmotoren (Motormanagement, Einspritzung, Zündung) erfordern so die garantierte Ausführung spezifischer Funktionen im unteren Mikrosekundenbereich [27]. Im Vergleich zu Mikrocontrollern gewährleisten FPGAs dabei die Funktionsausführung in allen Betriebszuständen eines Steuergerätes unter Beachtung der harten Echtzeitanforderungen. Auch können deutlich geringere Ausführungszeiten einzelner Funktionen realisiert werden.

Grafische Spezifikationsmethoden und damit einhergehende automatisierte Codegenerierung für Hardwarebeschreibungssprachen erleichtern die Integration rekonfigurierbarer Hardware in mechatronische Entwicklungsprozesse. Allerdings ist der Einsatz von FPGAs in mechatronischen Systemen meist kostenintensiver und aufwendiger als die Nutzung der Standardimplementierungsplattform Mikrocontroller. Ihre Vorteile wie Rechenleistung, Echtzeitfähigkeit und Hardwareflexibilität machen FPGAs dennoch zu einer günstigen Implementierungsplattform für die Steuer- und Regelfunktionalitäten vieler mechatronischer Systeme. Im Folgenden wird der Einsatz von FPGAs in verschiedenen Anwendungsgebieten an ausgewählten Beispielen erläutert. Die beschriebenen Systeme setzen keine partielle Rekonfiguration der FPGAs zur Abbildung von Funktionalitäten ein. Entsprechende Ansätze sind sehr selten und werden in Abschnitt 2.3 dieser Arbeit vorgestellt.

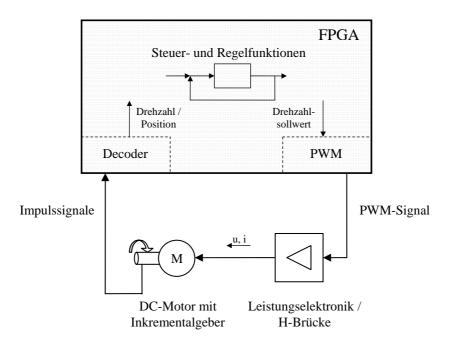

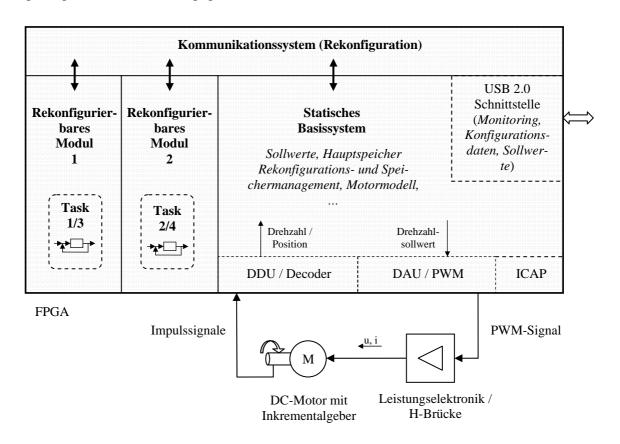

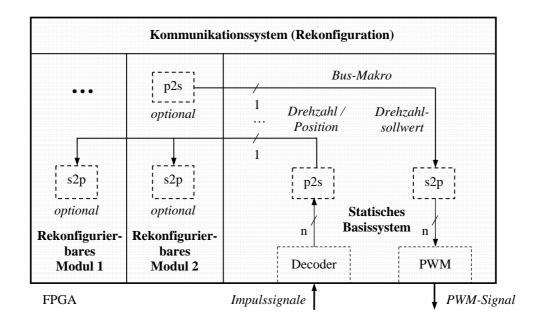

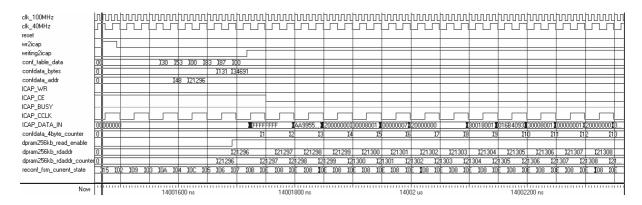

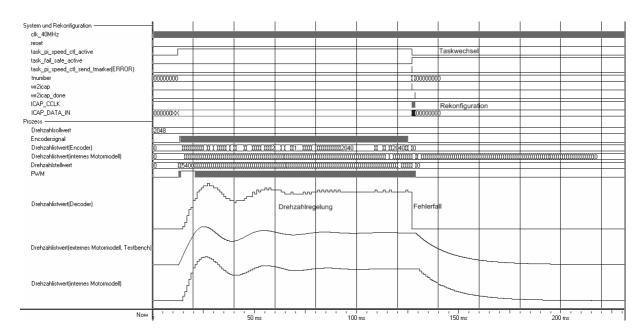

Eines der wichtigsten Anwendungsgebiete für FPGAs und zum Teil auch CPLDs in der Mechatronik ist die Regelung und Steuerung elektrischer Antriebe. Hier können mit FPGAs hohe Abtastraten und harte Echtzeitfähigkeit für digitale Regelungen elektrischer Maschinen realisiert werden. Abbildung 5 zeigt den schematischen Aufbau und die Komponenten eines einfachen FPGA-basierten drehzahlgeregelten Antriebssystems am Beispiel eines DC-Motors. Der Motor ist dabei mit einem Encoder zur Positions- und Drehzahlerfassung ausgestattet. Zum Einsatz kommen meist Inkrementalgeber, die über einen oder mehrere Kanäle jeweils ein periodisches Impulssignal übermitteln. Die Auswertung der Impulssignale und deren Umsetzung in Positions- und Drehzahlinformationen erfolgt in einem Decoder, der auf einer Auswertung der Flanken der Impulssignale basiert. Der Decoder kann im FPGA direkt in Hardware implementiert werden. Damit ergibt sich eine große Flexibilität bezüglich möglicher Abtastraten, Auflösungen und Einsatzfälle. Innerhalb des FPGAs erfolgt nun die für Steuerung und Regelung des Systems implementierte Signalverarbeitung, z.B. eine PI-Drehzahlregelung, und gibt die entsprechenden Stellsignale für die Drehzahl des Motors in digitaler Form aus. Diese werden dann über eine Pulweitenmodulation (PWM) auf ein Signal zur Ansteuerung der Leistungselektronik aufgeprägt. Die PWM-Komponente kann ebenfalls

sehr flexibel in Bezug auf Periodendauer (Auflösung) und Anwendungsfall direkt im FPGA in Hardware implementiert werden. Die Leistungselektronik außerhalb des FPGAs ist im Fall eines DC-Motors meist eine H-Brücke (Vierquadrantensteller) mit vier Schaltern, die angesteuert durch das PWM-Signal die mittlere Ankerspannung des DC-Motors und damit dessen Drehmoment und Drehzahl stellt. Für weitere Informationen zu elektrischen Antriebssystemen sei auf [32] verwiesen.

Abbildung 5: Schematischer Aufbau eines FPGA-basierten Antriebssystems mit DC-Motor

Ein Beispiel für die Implementierung von Decoder und PWM-Komponenten in FPGAs für die Ansteuerung von DC-Motoren wird in [33] beschrieben. Dort wird das eingebettete FPGA eines Atmel FPSLIC Mikrocontrollers für die flexible Hardwareumsetzung von mehreren Decoder- und PWM-Einheiten eingesetzt. Eine vollständig in FPGA-Hardware implementierte Antriebssteuerung für Asynchronmotoren auf der Basis von Xilinx FPGAs wird in [34] vorgestellt. Der Vorteil einer direkten FPGA-Implementierung ist hier die einfache Erweiterbarkeit des Systems um Komponenten wie Fehlererkennung und Benutzerschnittstellen. In modernen Antriebssystemen werden neben Asynchronmotoren und DC-Motoren häufig auch elektronisch kommutierte Synchronmaschinen, die so genannten bürstenlosen DC-Motoren (BLDC-Motoren), eingesetzt. Die komplexen Ansteuerungsalgorithmen dieser Antriebe können ebenfalls sehr gut auf FPGAs implementiert werden. So werden unter anderem in [35] und [36] Implementierungen von Controllern für BLDC-Motoren auf FPGAs beschrieben. Beide Quellen nutzen dazu Xilinx FPGAs und den eingebetteten Softcore-Mikroprozessor

MicroBlaze von Xilinx. Eine besondere Bedeutung im Kontext der Antriebssysteme kommt den Actel Fusion Mixed-Signal FPGAs zu. Diese verfügen über integrierte Analog-Digital-Wandler, die eine Messung von Motorstrom und Motortemperatur auch ohne zusätzliche externe Wandler ermöglichen [37]. Weiterhin bieten Actel Fusion FPGAs integrierte Treiberschaltungen für leistungselektronische Stellglieder.

Ein weiteres Anwendungsgebiet von FPGAs in mechatronischen Systemen stellen die Robotik und verwandte Domänen dar. Hier werden FPGAs vor allem für die direkte Implementierung untergeordneter Steuer- und Regelfunktionalitäten sowie die Kommunikation mit übergeordneten Systembestandteilen eingesetzt. Ein bekanntes Beispiel hierfür ist die mechatronische Hand des Deutschen Zentrums für Luft- und Raumfahrt [38]. Die Steuerung und Regelung dieses Systems erfolgt auf drei Ebenen. Auf der obersten Ebene befindet sich eine Kombination aus digitalem Signalprozessor als zentrale Recheneinheit und FPGA, das hier für die Kommunikation zuständig ist. Auf der mittleren Ebene, physisch durch ein Board in der Handfläche repräsentiert, übernimmt ein FPGA die komplexe Kommunikation und den Datentransfer zwischen der untersten und der oberen Ebene. Diese unterste Ebene der Hand sind die einzelnen Finger inklusive Sensorik und BLDC-Motoren als Antriebe. Auf dieser Ebene werden FPGAs in jedem einzelnen Finger für die Kommunikation mit den oberen Ebenen aber auch für die direkte Ansteuerung der Antriebe eingesetzt. Ein weiteres Beispiel für den Einsatz von FPGAs in der Robotik ist in [39] zu finden. Dort wird die Implementierung eines Fuzzy-Reglers für die adaptive Positionierung eines Gelenkes mit harten Nichtlinearitäten auf einem Xilinx FPGA beschrieben.

Ein drittes wichtiges Anwendungsgebiet für FPGAs in der Mechatronik ist das Rapid Control Prototyping, also die Entwicklung von Steuer- und Regelfunktionalitäten innerhalb einer Produktentwicklung. FPGAs bieten hier die Möglichkeit, eine konsistente Entwicklungsplattform für digitale Hardware in allen Entwicklungsphasen einzusetzen. Die implementierten Funktionen können durch eine statische Rekonfiguration der Hardware an verschiedene Entwicklungsschritte angepasst und beliebig erweitert werden. Der Einsatz eingebetteter Prozessorsysteme ergänzt diesen Ansatz um die Flexibilität von Software. So wird in [40] die Implementierung eines FPGA-basierten Rapid-Control-Prototyping-Systems für elektrische Antriebe beschrieben. Hier wird zusätzlich zur direkten Implementierung von Funktionen in Hardware ein Softcore-Mikroprozessor auf dem FPGA genutzt. Besonders interessant ist der Einsatz von FPGAs für die Funktionsentwicklung von Steuergeräten im Kraftfahrzeug (*Electronic Control Units*, ECUs). Ein Beispiel aus diesem Bereich wird in [41] vorgestellt. Das dort

beschriebene Entwicklungssteuergerät für die Motorsteuerung eines Motorrades basiert auf der CompactRIO-Plattform von National Instruments [42]. Die Hardwareplattform besteht aus einem Fließkommaprozessor für übergeordnete Regelfunktionen und flexibler FPGA-Hardware, die für die direkte Implementierung von aktornahen Regelfunktionen und für schnelle I/O-Funktionen eingesetzt wird. Die Verwendung der FPGA-Hardware ermöglicht den Funktionsentwicklern sehr hohe Abtastraten und eine hochdynamische Regelung der Verbrennungsvorgänge im Motor. Für die grafische Programmierung des Systems wird Lab-VIEW und das LabVIEW FPGA Modul von National Instruments genutzt [43].

### 2.3 Partielle Rekonfiguration von FPGAs

Die partielle Rekonfiguration von FPGAs ermöglicht den Austausch bzw. die Umprogrammierung von Teilen der Hardwarestruktur im laufenden Betrieb. Die Strukturvariabilität partiell rekonfigurierbarer Hardware bietet dabei völlig neue Ansätze für die Gestaltung und den Einsatz digitaler Hardware. Im Bereich der Mechatronik können so Controller realisiert werden, die ihre Hardwarestruktur und Parameter dynamisch an Betriebspunkte eines Systems anpassen, ohne alle benötigten Algorithmen parallel zu implementieren. Dadurch sinkt der Ressourcenbedarf der Implementierung. Weiterhin wird die Flexibilität der hardwarebasierten Controller stark erhöht, so dass aus der Softwaretechnik bekannte Prinzipien für den Entwurf angewendet werden können.

Das Potential der partiellen Rekonfiguration SRAM-basierter FPGAs wird bereits in [6] aus dem Jahr 1995 beschrieben. Die dort behandelten Architekturen waren sehr feingranular, so dass die Hardwarestruktur anhand von einzelnen Konfigurationsbits geändert werden konnte. Unter den heutigen auf dem Markt befindlichen Architekturen unterstützen insbesondere FPGAs von Xilinx die partielle Rekonfiguration. Xilinx bietet im Gegensatz zu anderen Herstellern Werkzeuge sowie Hardwareunterstützung für die Umsetzung partiell rekonfigurierbarer Funktionalitäten [44]. Aus diesem Grund befasst sich die überwiegende Mehrzahl der aktuellen Forschungs- und Entwicklungsprojekte zur partiellen Rekonfiguration von FPGAs mit Xilinx Bausteinen. Xilinx FPGAs sind auch die Zielplattform der in dieser Arbeit entwickelten rekonfigurierbaren Controller. Die folgenden Ausführungen zu Grundlagen, Werkzeugen und Umsetzung der partiellen Rekonfiguration beziehen sich daher direkt auf Xilinx FPGAs.

Auf weitere nach Herstellerangaben partiell rekonfigurierbare FPGA-Architekturen wie den Atmel FPSLIC/AT40K sowie die LatticeSC und Orca Bausteinen von Lattice sei an dieser Stelle nur der Vollständigkeit halber verwiesen ([20] [45] [46]).

#### 2.3.1 Hardwaregrundlagen

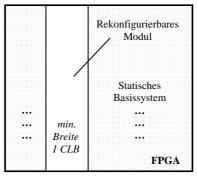

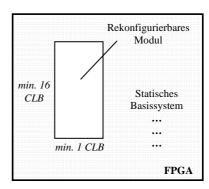

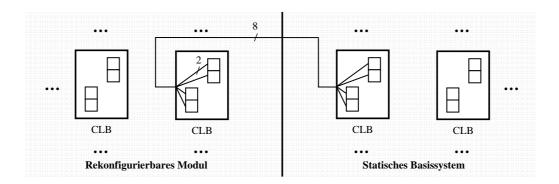

Die partielle Rekonfiguration von FPGAs setzt auf der Hardwareebene die Möglichkeit voraus, einzelne Bereiche der Architektur getrennt von anderen Bereichen umzuprogrammieren. Ausgehend von der Granularität ihrer Hardwarestruktur könnten SRAM-basierte FPGAs auf Bitebene konfiguriert werden. Allerdings bedingen die spezifischen Architekturen der Hersteller, dass der Konfigurationszugriff meist nur auf das ganze FPGA oder größere Teile davon möglich ist. Letzteres gilt für Xilinx FPGAs, die auf diese Weise partiell rekonfigurierbar sind. Die kleinsten einzeln programmierbaren Hardwareeinheiten auf Xilinx FPGAs werden als Frames bezeichnet. Die Größe und Anzahl der Frames ist dabei von der Bausteinfamilie und teilweise auch der Bausteingröße abhängig. So umfassen Frames der Virtex-II und Spartan-3 FPGAs immer Spalten über die ganze Höhe des FPGAs ([47] [48]). Die daraus abgeleiteten kleinsten praktisch rekonfigurierbaren Bereiche setzen sich aus mehreren Frames zusammen und werden durch einzelne Spalten oder Blöcke der Architektur repräsentiert. Die minimale Breite der Bereiche beträgt einen Configurable Logic Block (CLB), der wiederum aus vier Slices, den grundlegenden Logikblöcken von Xilinx FPGAs mit je zwei LUT und zwei Flipflops, besteht. Die kleinste einzeln rekonfigurierbare Einheit ist für Virtex-II und Spartan-3 FPGAs daher von der Größe des zugrunde liegenden Bausteins abhängig. Bei den moderneren Xilinx Virtex-4 FPGAs gilt die Beschränkung der kleinsten rekonfigurierbaren Bereiche auf Spalten der ganzen Länge des Bausteins nicht mehr. Hier können rechteckige Blöcke mit einer minimalen Höhe von 16 CLBs und einer minimalen Breite von einem CLB rekonfiguriert werden [49].

#### 2.3.2 Werkzeuge und Umsetzung

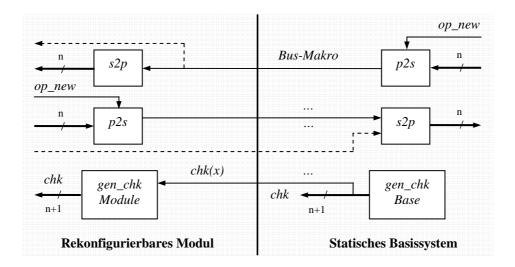

Für die Implementierung partiell rekonfigurierbarer Designs werden von Xilinx verschiedene Werkzeugketten und Verfahren bereitgestellt. Nur für kleine Änderungen eines Systems ist der Difference Based Partial Reconfiguration Design Flow geeignet [50]. Dabei werden die Datenstände zweier existierender Konfigurationsdatensätze (Bitstreams) verglichen und die Differenz als partieller Bitstream für die Rekonfiguration verwendet. Für den Austausch ganzer Hardwarebereiche kann der Early Access Partial Reconfiguration Design Flow (EAPR Design Flow) eingesetzt werden [51]. Dieser wurde aus dem älteren Module Based Partial Reconfiguration Design Flow entwickelt und basiert auf einer Aufteilung des Designs in einen statischen sowie einen oder mehrere partiell rekonfigurierbare Bereiche [52]. Die Kommunikation zwischen rekonfigurierbaren und statischen Bereichen eines Designs wird dabei über so genannte Bus-Makros realisiert. Sie sind mit Hilfe von LUTs und Routingressourcen

implementierte persistente Verbindungen, die von einer Rekonfiguration nicht betroffen sind. Für den EAPR Design Flow kommen modifizierte Implementierungswerkzeuge von Xilinx zum Einsatz, die initiale Konfigurationsdatensätze für den ganzen FPGA und partielle Bitstreams für die rekonfigurierbaren Bereiche erzeugen. Die Vorgehensweise ist skriptbasiert, eine ergänzende grafische Unterstützung wird in [53] vorgestellt.

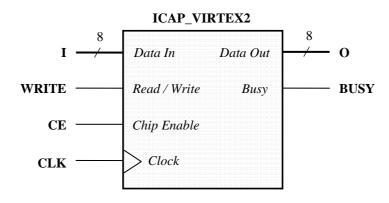

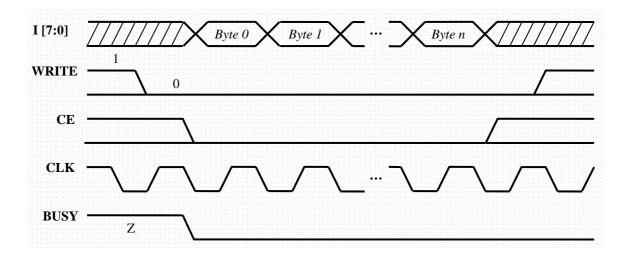

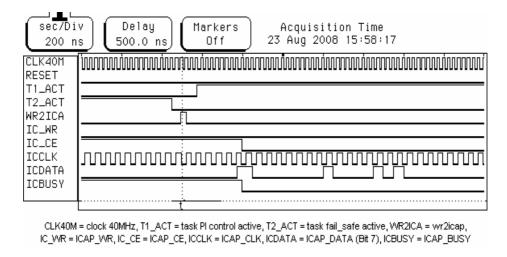

Auf der Hardwareebene erfolgt die Umsetzung der partiellen Rekonfiguration für den Nutzer durch die Übermittlung der erzeugten partiellen Bitstreams an die Konfigurationsschnittstellen des FPGAs. Der Großteil der Konfigurationsschnittstellen muss von externen Quellen gesteuert werden. Eine Ausnahme ist der in Xilinx FPGAs eingebettete *Internal Configuration Access Port* (ICAP), der die Selbstrekonfiguration eines Systems ermöglicht [54]. Weitere Informationen zu Vorgehensweisen und Werkzeugen finden sich unter anderem in [4]. Kapitel 5 dieser Arbeit geht näher auf Hardwaregrundlagen, Implementierungsverfahren, Werkzeuge und Konfigurationsschnittstellen ein.

### 2.3.3 Anwendungen

Ein wichtiges Anwendungsgebiet für die partielle Rekonfiguration von FPGAs ist die Bildund Videoverarbeitung. So wird in [55] mit der Sonic-on-a-Chip-Architektur eine modulare

Plattform für die Videoverarbeitung beschrieben, die unter Ausnutzung der partiellen Rekonfiguration auf Xilinx FPGAs implementiert wurde. In [56] wird dagegen ein video-basiertes

Fahrerassistenzsystems für Kraftfahrzeuge vorgestellt. Während die obere Ebene des Systems

durch einen im FPGA eingebetteten Prozessor realisiert wird, werden auf untere Ebene Hardwarebeschleuniger für die Bildverarbeitung mittels partieller Rekonfiguration ausgetauscht.

Ein ebenfalls wichtiger Anwendungsbereich ist *Software-defined Radio* (SDR) [53]. Die partielle Rekonfiguration von FPGAs ermöglicht in SDR-Systemen eine flexible Anpassung der

Hardware an verschiedene drahtlose Datenübertragungsverfahren [57]. Für diesen Anwendungsbereich wird von Xilinx und iSR Technologies bereits eine Entwicklungsplattform auf

der Basis von Xilinx Virtex-4 FPGAs angeboten [58]. Weitere Anwendungsgebiete, wie

adaptive Kryptographiesysteme und Hochleistungsrechner, werden unter anderem in [4] dargestellt.

Im Bereich der Mechatronik gibt es bisher nur wenige Ansätze zur Ausnutzung der partiellen Rekonfiguration von FPGAs. Bereits im Jahr 2002 wurde in [59] ein Fail-Safe-System für Steuergeräte in Kraftfahrzeugen vorgestellt, das auf der partiellen Rekonfiguration von älteren Xilinx XC6200 FPGAs basiert. Diese Architekturen verfügten nur über beschränkte Logikres-

sourcen und waren sehr feingranular aufgebaut. In [60] und [4] wird weiterhin ein theoretischer Ansatz für die Implementierung adaptiver Controller auf partiell rekonfigurierbarer Hardware beschrieben. Besonderes Merkmal ist hier der Einsatz zweier rekonfigurierbarer Controllermodule, von denen jeweils nur eines aktiv ist. Eine Hauptsteuereinheit realisiert das Umschalten und die Rekonfiguration der Module.

#### 2.3.4 Weiterführende Ansätze

Der Einsatz der partiellen Rekonfiguration von FPGAs wird durch Randbedingungen und Voraussetzungen heutiger Implementierungssoftware und FPGA-Hardware teilweise eingeschränkt. So gibt es bei aktuellen Implementierungsverfahren immer einen gewissen Überhang an Konfigurationsdaten und -aufwand, der sich aus einer unnötigen Umprogrammierung von Teilen der Hardware ergibt. Ansätze zur Minimierung des Rekonfigurationsüberhangs und damit zu effizienteren Rekonfigurationsmethoden werden unter anderem in [61], [62] und [63] vorgestellt. Die Verteilung der I/O-Pins und deren Zuordnung zu bestimmten Schnittstellen auf aktuellen FPGAs und FPGA-Entwicklungsboards sind ebenfalls problematisch. Hier setzt die in [64] und [4] beschriebene ESM-Plattform an, auf der die Verbindung von rekonfigurierbaren Bereichen zu I/O-Pins durch einen speziellen Interfacecontroller realisiert wird. Weiterhin wird eine freie Umplatzierung (Reallokation) von rekonfigurierbaren Funktionen auf dem FPGA durch heutige Hardware und Implementierungsverfahren noch nicht unterstützt und ist daher Gegenstand aktueller Forschung und Entwicklung. Für weiterführende Informationen zu diesem und anderen aktuellen Forschungsthemen wie temporaler Platzierung und Schedulingalgorithmen sei auf [4] verwiesen.

### 2.4 Bitserielle Signalverarbeitung

Für die Implementierung von Steuer- und Regelfunktionen in rekonfigurierbarer FPGA-Hardware wird in dieser Arbeit auch bitserielle Signalverarbeitung nach [65] eingesetzt. Gegenüber herkömmlichen bitparallelen Ansätzen verfügt die bitserielle Signalverarbeitung über eine bessere Skalierbarkeit und einen geringeren Logikaufwand. Grundlegender Gedanke der bitseriellen Informationsverarbeitung ist die Übertragung eines Operanden im Zeitmultiplex auf nur einer Leitung. Die so sehr niedrige Komplexitätsebene ermöglicht eine intensive Nutzung von Pipelineeffekten. Während bei bitparallelen Ansätzen eine Erhöhung der Verarbeitungswortbreite immer eine Steigerung des Gatterbedarfs bedeutet, führt dies bei bitseriellen Methoden lediglich zu einer Vergrößerung der Bearbeitungs- und Übertragungszeit. Dabei

hängt die mögliche Abtastfrequenz  $f_S$  direkt von der Wortbreite n ab und begrenzt sie nach oben entsprechend der Taktfrequenz  $f_C$ . Es gilt:

$$f_{S \max} = \frac{f_C}{n}$$

Gleichung 2-1

Allerdings erlauben moderne FPGAs Taktfrequenzen von mehreren 100 MHz, so dass sich für die Implementierung mechatronischer Steuer- und Regelfunktionen kein Nachteil durch die Reduzierung der Abtastfrequenz ergibt.

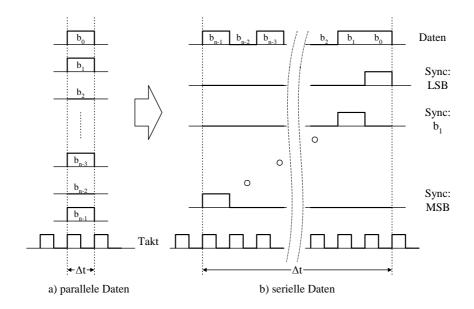

Da arithmetische Algorithmen immer von einer bekannten Gewichtung der Operandenbits ausgehen, wird für die bitserielle Signalverarbeitung nach [65] eine Kennzeichnung aller Bits durch ein getrennt zu übertragendes Synchronsignal implementiert. Das Synchronsignal wird durch einen Bus mit einer der Verarbeitungswortbreite entsprechenden Breite realisiert. Dieses Prinzip wird in Abbildung 6 verdeutlicht. Dabei muss zusätzlich jedem Operator innerhalb der bitseriellen Signalverarbeitungskette die durch vorhergehende Operatoren verursachte Verzögerung des Datenstroms bekannt gegeben werden. Die Verzögerung wird manuell oder automatisiert mit einer Strukturanalyse vor der Implementierung ermittelt [66].

Abbildung 6: Synchronisationssignale bitserieller Signalverarbeitung nach [65]

Für weitere Informationen zu Grundlagen bitserieller Signalverarbeitung sei auf [65] verwiesen. Abschnitt 5.1.2 dieser Arbeit geht auf die Einsatzmöglichkeiten und Vorteile bitserieller Signalverarbeitung in partiell rekonfigurierbaren Systemen ein.

### 3 Entwurfsmethodik

Dieses Kapitel der Arbeit stellt eine universelle Entwurfsmethodik für rekonfigurierbare Controller in mechatronischen Systemen vor. Ausgehend von allgemeinen Entwurfsmethoden für Steuer- und Regelfunktionalitäten mechatronischer Systeme wird eine Methodik entwickelt, die sich in bestehende Vorgehensweisen integriert und diese um Abbildungsmöglichkeiten für partiell rekonfigurierbare Hardwarefunktionen ergänzt. Dabei werden allgemeingültige Spezifikationsmittel und Werkzeuge eingesetzt. Besonderes Merkmal der hier vorgestellten Entwurfsmethodik ist die implizite Definition und Integration eines Rekonfigurationsmanagements. Dieses ergibt sich aus einer Partitionierung von Funktionalitäten in statische und rekonfigurierbare Hardwareanteile und ermöglicht eine hardwareunabhängige Berücksichtigung von Rekonfigurationsvorgängen schon zu frühen Entwicklungszeitpunkten. Die eingesetzten Spezifikationsmittel unterstützen hierbei eine verteilte Implementierung des Rekonfigurationsmanagements sowie eine echtzeitfähige Lade- und Aktivierungstrategie für rekonfigurierbare Hardwarefunktionen.

Der erste Abschnitt des Kapitels beschreibt die grundlegenden Methoden und Werkzeuge der Entwurfsmethodik und deren Einbindung in bestehende Vorgehensweisen. Daraufhin wird im zweiten Abschnitt die Partitionierung von rekonfigurierbaren Controllern und Hardwarefunktionen auf Funktions- und Hardwareebene erläutert. Der dritte Teil des Kapitels geht näher auf das verteilte Rekonfigurationsmanagement, dessen implizite Spezifikation und abschließend auf Lade- und Aktivierungsstrategien für Hardwarefunktionen ein.

### 3.1 Entwurfsgrundlagen

Der Entwurf von Steuer- und Regelfunktionalitäten für mechatronische Systeme erfolgt heute zumeist im Kontext übergeordneter Vorgehensweisen für die System- und Produktentwicklung. Insbesondere das aus der Softwareentwicklung stammende V-Modell wird für die Be-

schreibung und Modellierung der Entwurfsprozesse eingesetzt. Mit einem der Systementwicklung untergeordnetem V-Modell können daher die Entwurfsschritte für rekonfigurierbare Controller in die Entwicklungsprozesse mechatronischer Systeme eingebunden werden. Ein entsprechender Ansatz wird in diesem Abschnitt beschrieben. Ein weiterer Schwerpunkt der hier vorgestellten Entwurfsgrundlagen sind die innerhalb der Entwicklungsprozesse angewandten Spezifikationsmittel und Spezifikationswerkzeuge für rekonfigurierbare Controller und deren Funktionalitäten. Dabei werden ausgehend von bestehenden Softwarewerkzeugen grafische Spezifikationsmittel für Steuer- und Regelfunktionen eingesetzt, die sowohl in der Software- als auch der digitalen Hardwareentwicklung Anwendung finden. Dieser Ansatz unterstützt die Integration partiell rekonfigurierbarer Hardware in Entwicklungsprozesse mechatronischer Systeme.

### 3.1.1 Vorgehensmodell

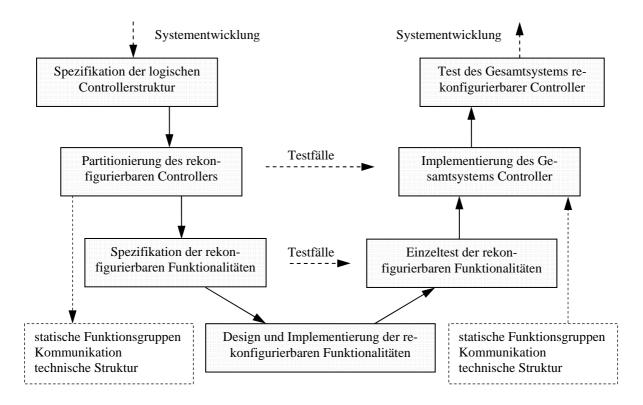

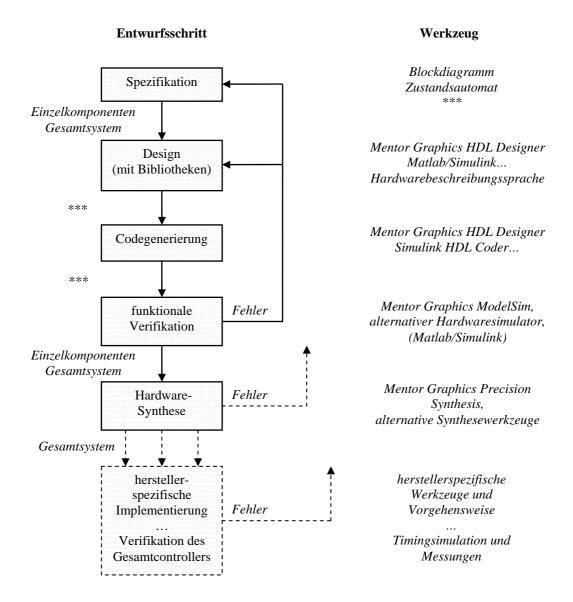

Die Vorgehensweise für den Entwurf rekonfigurierbarer Controller in der Mechatronik kann durch einen Unterzweig eines V-Modells der Systementwicklung beschrieben werden. Ausgehend von dem in Abschnitt 2.1 vorgestellten Teil-V-Modell für die Softwareentwicklung von Kraftfahrzeugsteuergeräten nach [26] wird hier beispielhaft ein Teil-V-Modell für rekonfigurierbare Controller mit Fokus auf die partiell rekonfigurierbaren Funktionalitäten vorgestellt.

Wie in Abbildung 7 dargestellt schließt sich der Unterzweig für rekonfigurierbare Controller an die übergeordnete Ebene der Systementwicklung mit dem Teilschritt der Spezifikation der logischen Controllerstruktur an. Dabei wird ein abstraktes Funktionsmodell des Controllers entworfen, das die Struktur und die Vernetzung der einzelnen Teilfunktionen beschreibt. Dieser Schritt ist unabhängig von der späteren Zielplattform und Hardware. Im nächsten Schritt des Teil-V-Modells erfolgt die Partitionierung der einzelnen Controllerfunktionen in statische und partiell rekonfigurierbare Bestandteile. Die Partitionierung auf Funktionsebene bedingt bereits eine Berücksichtigung der partiellen Rekonfigurierbarkeit der Zielplattform, ist jedoch ansonsten unabhängig von der realen Ausprägung der Hardware. Im Anschluss an die Partitionierung werden getrennte Entwurfsschritte für statische und rekonfigurierbare Funktionsgruppen, die Kommunikation zwischen den Controllerbestandteilen und die Abbildung der technischen Controllerstruktur auf eine bestimmte Hardware durchlaufen. In Abbildung 7 werden aus Übersichtsgründen nur die Entwurfsschritte für rekonfigurierbare Funktionalitäten gezeigt. Diese umfassen Spezifikation, Design, Implementierung und Test der rekonfigurierbaren Funktions-

gruppen in der Implementierung des Gesamtsystems rekonfigurierbarer Controller und abschließend dessen Test. Die Teilschritte der Partitionierung des Controllers sowie die Spezifikation der rekonfigurierbaren Funktionalitäten ermöglichen dabei die implizite Integration eines verteilten Rekonfigurationsmanagements, das in Abschnitt 3.3 vorgestellt wird.

Abbildung 7: Untergeordnetes V-Modell für den Entwurf rekonfigurierbarer Controller

### 3.1.2 Spezifikationswerkzeuge

Die Entwicklung von Steuer- und Regelfunktionalitäten für mechatronische Systeme erfolgt zumeist mit Softwarewerkzeugen, die eine getrennte grafische Spezifikation von Kontroll- und Datenfluss unterstützen. Zum Einsatz kommen unter anderem Werkzeuge wie Matlab/Simulink der Firma The Mathworks, LabVIEW von National Instruments und ASCET der ETAS GmbH. Der Kontrollfluss wird dabei oft durch Zustandsautomaten abgebildet, deren Steuersignale einen durch Blockdiagramme repräsentierten Datenfluss beeinflussen. Die Spezifikationsmittel der verschiedenen Werkzeuge ermöglichen so eine implementierungsunabhängige Beschreibung von Steuer- und Regelfunktionen und erlauben zum Teil eine Überführung der erstellten Spezifikationsmodelle in Produktionssoftware. Ausgehend davon werden in dieser Arbeit ebenfalls allgemeingültige und hardwareunabhängige grafische Spezifikationsmittel für die Abbildung von Struktur und Verhalten rekonfigurierbarer Funktionalitäten genutzt.

Der Datenfluss rekonfigurierbarer Steuer- und Regelfunktionen in mechatronischen Systemen wird in der vorliegenden Arbeit vorwiegend mit Blockdiagrammen spezifiziert. Blockdiagramme bestehen aus Signalverbindungen, die den eigentlichen Datenfluss repräsentieren, und Blöcken, die Funktionen abbilden. Die Funktionsblöcke eines Blockdiagramms können neben grundlegenden Signalverarbeitungselementen auch weitere Blockdiagramme beinhalten. Weiterhin können Funktionsblöcke andere Spezifikationsformen wie Wahrheitstabellen, Zustandsautomaten und Programmiersprachen integrieren. Dabei verfügen alle Funktionsblöcke über definierte Schnittstellen, die sich in Eingänge und Ausgänge unterscheiden. Auf diese Weise können rekonfigurierbare Funktionalitäten hierarchisch gegliedert und so übersichtlich strukturiert werden. Die oberste Ebene (Top-Level) definiert dann die Schnittstellen eines rekonfigurierbaren Controllers oder einer rekonfigurierbaren Funktion innerhalb eines Controllers, während die niedrigste Ebene elementare Algorithmen abbildet.

Der Kontrollfluss rekonfigurierbarer Steuer- und Regelfunktionen in mechatronischen Systemen wird für die vorliegende Arbeit dagegen mit Zustandsautomaten spezifiziert. Zustandsautomaten bestehen aus Zuständen und Transitionen, den Übergängen zwischen Zuständen. Die Transition zwischen zwei Zuständen erfolgt abhängig von bestimmten Bedingungen, die dem Ausgangszustand zugeordnet sind. Die einzelnen Zustände enthalten spezifische Funktionen, die durch ihre Zustandsaktionen festgelegt sind. Zustandsaktionen können dabei unter anderem mit Blockdiagrammen spezifiziert werden. Auch den Transitionen kann eine spezifische Funktion, die Übergangsaktion, zugeordnet werden. Weiterhin können einzelne Zustände untergeordnete Zustandsautomaten beinhalten, so dass hierarchische Automaten entstehen.

Die Spezifikationsmodelle für Kontroll- und Datenfluss werden in dieser Arbeit mit Softwarewerkzeugen erstellt, die eine Überführung in Hardwarebeschreibungssprachen wie VHDL oder Verilog gestatten. Die abstrakte Beschreibung mit grafischen Mitteln und nachfolgender Codegenerierung erleichtert den Zugang zu programmierbarer Hardware. Primäres Spezifikations- und Codegenerierungswerkzeug ist der HDL Designer von Mentor Graphics [67], der Blockdiagramme, Zustandsautomaten sowie weitere Spezifikationsformen unterstützt ([68] [69]). Der HDL Designer wird darüber hinaus als Plattform für ein übergreifendes Spezifikationsframework genutzt, das in Abschnitt 4.3 näher beschrieben wird. Weiterhin wird Matlab/Simulink in Verbindung mit dem Simulink HDL Coder für die Spezifikation, Simulation und Codegenerierung einzelner Controllerbestandteile eingesetzt [70]. Die aktuelle Version des Simulink HDL Coders unterstützt die Codegenerierung jedoch nur für eine Untergruppe elementarer Funktionsblöcke. Hier nicht verwendete Alternativen zu den ge-

nannten Spezifikations- und Codegenerierungswerkzeugen sind der ebenfalls in Matlab/Simulink integrierte System Generator for DSP von Xilinx [71], das LabVIEW FPGA Modul von National Instruments [43] und spezifische grafische Editoren einzelner FPGA-Hersteller.

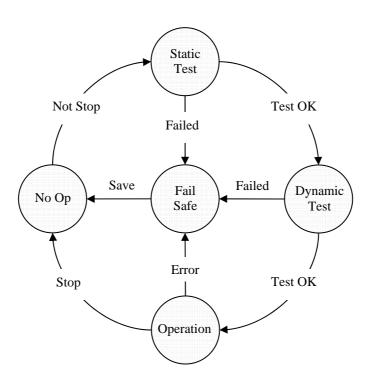

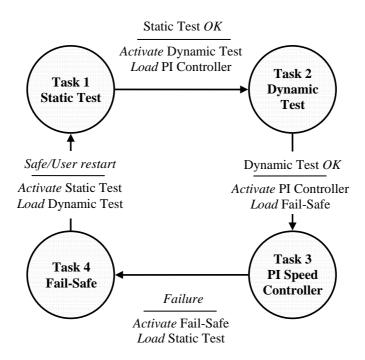

Abbildung 8: Zustandsautomat für Hochlauf und Betrieb eines mechatronischen Systems

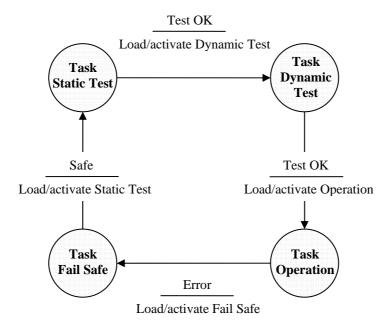

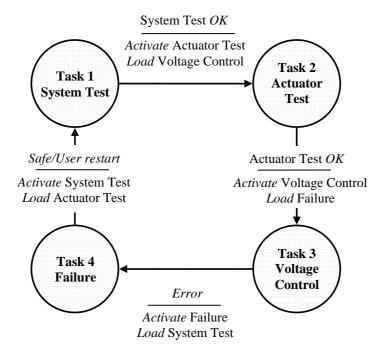

### 3.1.3 Spezifikation der logischen Controllerstruktur mit Zustandsautomaten

Der Einsatz von Zustandsautomaten für die Spezifikation mechatronischer Steuer- und Regelfunktionen basiert auf einer engen Verknüpfung zwischen Kontroll- und Datenfluss. Die logische Struktur eines mechatronischen Controllers mit Betriebszuständen, Ablaufsteuerungen und Funktionswechseln kann durch die Zuordnung von Blockdiagrammen und anderen Funktionsbeschreibungen zu den Zuständen eines Automaten sehr effizient abgebildet werden. Abbildung 8 zeigt einen beispielhaften Zustandsautomaten, der den Hochlauf und den Betrieb eines mechatronischen Systems kontrolliert und so dessen logische Controllerstruktur definiert. Ausgehend von statischen und dynamischen Tests, die auch Aktorik und Sensorik betreffen können, wird das System in den Hauptbetriebszustand gebracht. Im Fehlerfall werden die Testvorgänge und der Hauptbetriebszustand verlassen, um das System in einen sicheren Zustand (Fail Safe) zu bringen. Der Neustart des Systems bedingt den Wechsel in einen passiven Zustand (No Op). Die Spezifikation der einzelnen Betriebszustände erfolgt mit Datenflussbeschreibungen wie Blockdiagrammen, während die Spezifikation des übergeordneten

Systemverhaltens auf einem Zustandsautomaten basiert. Eine Erweiterung dieser Methodik auf rekonfigurierbare Hardware ermöglicht den Einsatz von Zustandsautomaten zur Spezifikation von Lade- und Aktivierungsvorgängen für rekonfigurierbare Steuer- und Regelfunktionalitäten. Ein entsprechender Ansatz zur Verbindung von Spezifikation, Rekonfigurationsmanagement und Strukturvariabilität wird in den folgenden Abschnitten vorgestellt.