# Architecting a Pluggable Query Executor for Emerging Co-Processors

#### **DISSERTATION**

zur Erlangung des akademischen Grades

Doktoringenieur (Dr.-Ing.)

angenommen durch die Fakultät für Informatik der Otto-von-Guericke-Universität Magdeburg

von M.Sc. Balasubramaninan Gurumurthy

geb. am 03.10.1992

in Neyveli

Gutachterinnen/Gutachter

Prof. Dr. rer. nat. habil. Gunter Saake

Prof. Dr.-Ing. Thilo Pionteck

Prof. i. R. Dr. Klaus Meyer-Wegener

Magdeburg, den 25.01.2024

# **Abstract**

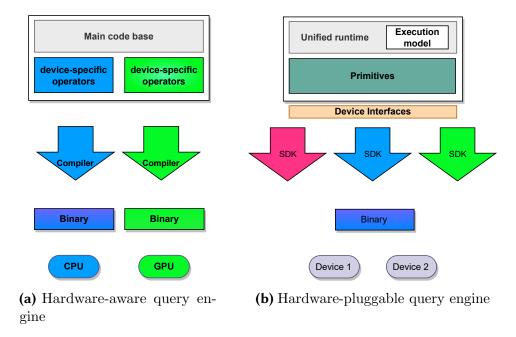

CPUs are reaching their scaling limitations while data keeps growing rapidly. Developers of CPU-based applications are searching for an alternative processor to further improve their efficiency. DBMS being one such application, is always in need of high-performing processors to support the ever-growing data. Therefore, many database researchers investigate various co-processors available in the market to speed up query processing. As a result, many such co-processor accelerated DBMS engines are available both as commercial as well as research projects. Such a DBMS running on a co-processor is normally developed by tightly integrating the hardwarerelevant code within the query execution engine. Or, the query engine is written with a common device-agnostic framework (like OpenCL) to support execution on different co-processor architectures. Out of these approaches, the former takes a lot of effort to develop, and the latter is not performance-portable. Additionally, with every new co-processor available in the market, an effort has to be made to develop a query engine on top of this device. Hence, to overcome these challenges, in this thesis, we explore a query executor that lies in the middle ground between the two approaches. Our query engine splits DBMS operators into primitives which are present in a task layer. This layer in addition to the device layer enables the pluggability of co-processors. Further, to reduce implementation effort, we also come up with a unified runtime, that handles query execution across any abstract co-processor. Overall, in this work, we explore a query engine that is capable of plugging in any new co-processor that comes up in the future, without losing the capability to have an optimal implementation over the device.

# Zusammenfassung

Unter rapide steigenden Datenmengen stoßen CPUs an ihre Skalierungsgrenzen. Anwendungen, die auf herkömmlichen CPUs laufen, sind auf der Suche nach einem alternativen, spezialisierten Prozessoren, um ihre Effizienz weiter zu verbessern. Datenbankmanagementsysteme sind eine solche Anwendung, die immer leistungsstärkere Prozessoren benötigen, um die ständig wachsenden Datenmengen zu verarbeiten. Daher untersuchen viele Datenbankforscher verschiedene auf dem Markt erhältliche Co-Prozessoren, um die Abfrageverarbeitung zu beschleunigen. Infolgedessen sind viele solcher Co-Prozessor-beschleunigten Datenbank-Engines sowohl als kommerzielle als auch als Forschungsprojekte verfügbar. Ein solches Datenbankmanagementsystem, das auf einem Co-Prozessor läuft, wird normalerweise mit einer engen Integration des Hardware-Codes in die Anfrageausführungs-Engine entwickelt. Alternativ wird die Anfrage-Engine mit einem gemeinsamen geräteunabhängigen Wrapper (wie OpenCL) geschrieben, um die Ausführung auf verschiedenen Co-Prozessor-Architekturen zu unterstützen. Von diesen Ansätzen ist der erste sehr aufwändig in der Entwicklung und der zweite ist nicht leistungsfähig genug. Außerdem muss mit jedem neuen Co-Prozessor, der auf dem Markt verfügbar ist, eine Abfrage-Engine für dieses Gerät entwickelt werden. Um diese Herausforderungen zu überwinden, erforschen wir in dieser Arbeit eine Datenbank-Engine, die in der Mitte zwischen diesen beiden Ansätzen liegt. Unsere Abfrage-Engine teilt Datenbank-Operatoren in Primitive auf, die in einer Aufgabenschicht vorhanden sind. Diese Schicht ermöglicht zusammen mit der Geräteschicht das Plug'n'Play von Co-Prozessoren. Um den Implementierungsaufwand zu verringern, haben wir außerdem eine einheitliche Laufzeit entwickelt, die die Ausführung von Abfragen auf jedem abstrakten Co-Prozessor ermöglicht. Insgesamt entwickeln wir in dieser Arbeit eine Abfrage-Engine, die in der Lage ist, jeden neuen Co-Prozessor, der in der Zukunft auftaucht, einzubinden, ohne die Fähigkeit zu verlieren, eine optimale Implementierung für den Prozessor zu bieten.

# **Contents**

| 1 | Intr | oductio | on                                                  | 1  |

|---|------|---------|-----------------------------------------------------|----|

|   | 1.1  | The N   | eed for Hardware-Awareness in DBMS                  | 2  |

|   | 1.2  | Challe  | enges in Hardware & SDK Trends                      | 3  |

|   | 1.3  | DBMS    | S over Heterogeneous Co-Processors                  | 4  |

|   | 1.4  | Goal    | of this Thesis                                      | 4  |

|   | 1.5  | Contr   | ibutions: Three Tiers of a Pluggable Query Executor | 5  |

|   | 1.6  | Corres  | sponding Publications                               | 7  |

|   | 1.7  |         | ne of this Thesis                                   | 8  |

| 2 | Tier | 0: Cur  | rent Co-Processor Ecosystem                         | 9  |

|   | 2.1  | Curre   | nt Generation Co-Processors                         | 10 |

|   | 2.2  | Progra  | amming Co-Processors                                | 17 |

|   |      | 2.2.1   | Programming Paradigms                               | 17 |

|   |      | 2.2.2   | Programming APIs                                    | 18 |

|   | 2.3  | Abstra  | action Models                                       | 22 |

|   |      | 2.3.1   | Skeleton-Based Systems                              | 25 |

|   |      | 2.3.2   | Task-Based Systems                                  | 27 |

|   | 2.4  | Challe  | enges in DBMS with Co-Processors                    | 28 |

|   |      | 2.4.1   | Device Features                                     | 29 |

|   |      | 2.4.2   | Abstraction Hierarchy                               | 29 |

|   |      | 2.4.3   | Parallelism Complexity                              | 29 |

|   |      | 2.4.4   | Optimization Strategies                             | 30 |

|   | 2.5  | Oppor   | rtunities for Query Execution                       | 30 |

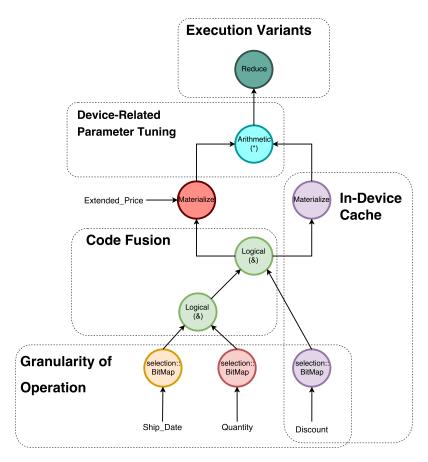

|   |      | 2.5.1   | Granularity of Operation                            | 32 |

|   |      | 2.5.2   | Code Fusion                                         | 32 |

|   |      | 2.5.3   | In-Device Cache                                     | 32 |

|   |      | 2.5.4   | Execution Variants                                  | 33 |

|   |      | 2.5.5   | Device-Related Parameter Tuning                     | 33 |

|   | 2.6  | Summ    | nary                                                | 33 |

| 3 | Exis | ting U  | nified Runtime                                      | 35 |

|   | 3.1  | DBMS    | S On Co-Processors                                  | 36 |

|   | 3.2  | Existir | ng Abstract Runtime                                 | 37 |

|   |      | 3.2.1   | Skeleton-Based                                      | 37 |

|   |      | 3.2.2   | Component-Based                                     | 40 |

|   | 3.3  | Summ    | nary                                                | 42 |

| 4 | Tier | 0/1· C  | rafting a Co-Processor Aware DRMS Operator          | 43 |

viii Contents

|   | 4.1  | Need for HW-Awareness in Group-By                  | 43 |

|---|------|----------------------------------------------------|----|

|   | 4.2  | Related Work                                       | 46 |

|   | 4.3  | GPU and Atomic Functions                           | 46 |

|   |      | 4.3.1 Architectural Components Involved            | 47 |

|   |      | 4.3.2 Profiling Atomic Operations                  | 47 |

|   | 4.4  | Atomics within Sort-Based Aggregation              | 49 |

|   |      | 4.4.1 Sort-Based Aggregation on a GPU: A Primer    | 49 |

|   |      | 4.4.2 Minimizing Atomics Using Private Space       | 50 |

|   | 4.5  | Experiments                                        | 51 |

|   |      | 4.5.1 Micro Benchmark                              | 52 |

|   |      | 4.5.2 Comparative Experiments                      | 54 |

|   | 4.6  | Summary                                            | 59 |

| 5 | Tier | 1: Primitive Definitions for Interfacing Operators | 61 |

|   | 5.1  | Defining Primitives                                | 62 |

|   | 5.2  | Atomic Primitives                                  | 63 |

|   |      | 5.2.1 Map                                          | 63 |

|   |      | 5.2.2 Scan                                         | 64 |

|   |      | 5.2.3 Reduce / Aggregate                           | 65 |

|   |      | 5.2.4 Scatter & Gather                             | 66 |

|   | 5.3  | Composed Primitives                                | 66 |

|   |      | 5.3.1 Filter                                       | 66 |

|   |      | 5.3.2 Materialize                                  | 67 |

|   |      | 5.3.3 Hash Build                                   | 68 |

|   |      | 5.3.4 Hash Probe                                   | 69 |

|   |      | 5.3.5 Split                                        | 69 |

|   |      | 5.3.6 Sort                                         | 70 |

|   | 5.4  | Other Impact Factors                               | 70 |

|   |      | 5.4.1 Access Pattern                               | 70 |

|   |      | 5.4.2 Parallelism Mode                             | 71 |

|   |      | 5.4.3 Data Structure                               | 71 |

|   | 5.5  | Primitive-Based Execution in a Query Engine        | 71 |

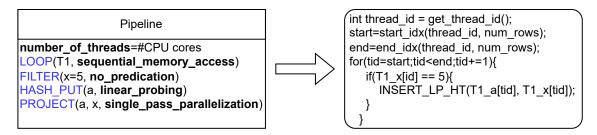

|   |      | 5.5.1 Pipeline Patterns                            | 72 |

|   | 5.6  | Summary                                            | 73 |

| 6 | Tier | 1: Task Layer - Realizing Standard Primitives      | 75 |

|   | 6.1  | GPU Libraries within DBMS                          | 76 |

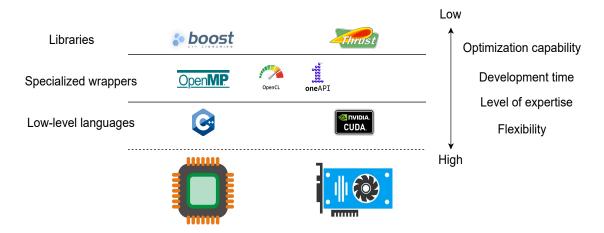

|   | 6.2  | Levels of Programming Abstractions                 | 77 |

|   | 6.3  | Implementing DBMS Operators With Libraries         | 78 |

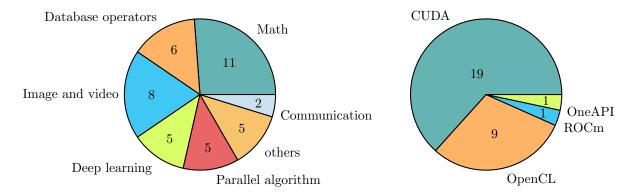

|   |      | 6.3.1 Review of GPU Libraries                      | 78 |

|   |      | 6.3.2 Operator Realization                         | 80 |

|   |      | 6.3.3 Summary of Library Usefulness                | 80 |

|   | 6.4  | A Connecting Framework for Library Operators       | 81 |

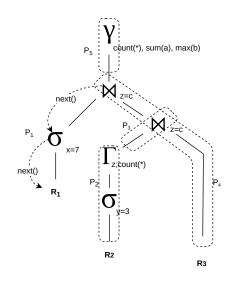

|   |      | 6.4.1 Task Model                                   | 81 |

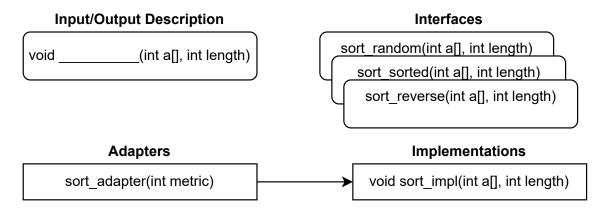

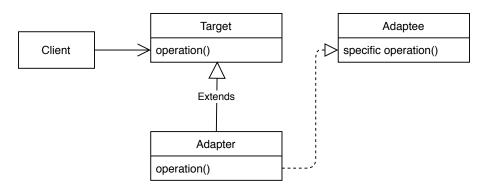

|   |      | 6.4.2 Adapter Pattern                              | 81 |

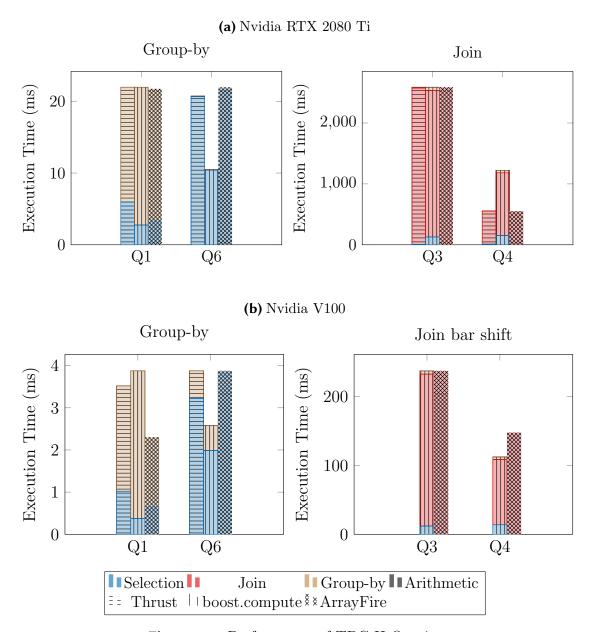

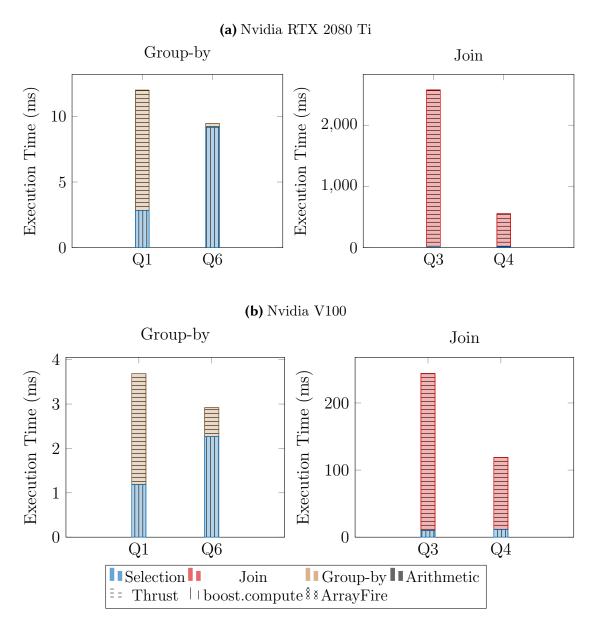

|   | 6.5  | Performance Comparison                             | 82 |

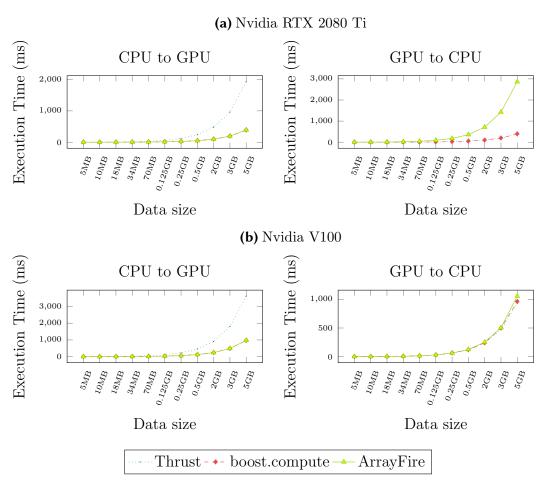

|   |      | 6.5.1 Transfer Time                                | 83 |

|   |      | 6.5.2 Micro-Benchmark: Individual Operators        | 84 |

Contents

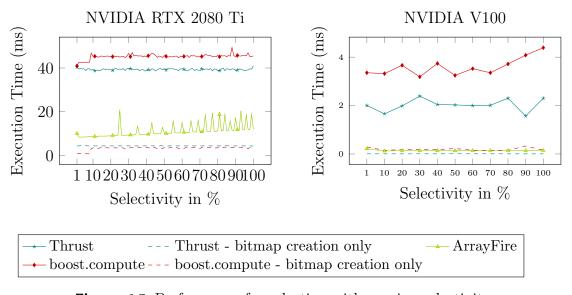

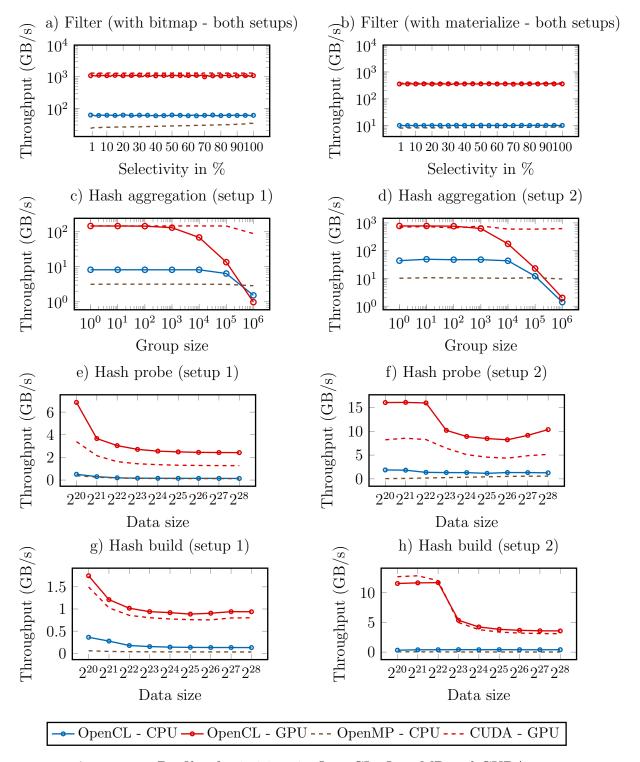

|   |      |        | 6.5.2.1 <b>Selection</b>                                      | . 84  |

|---|------|--------|---------------------------------------------------------------|-------|

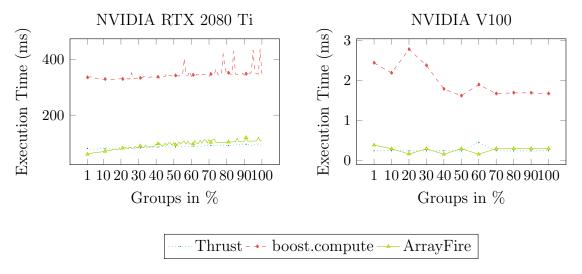

|   |      |        | 6.5.2.2 <b>Group By</b>                                       | . 85  |

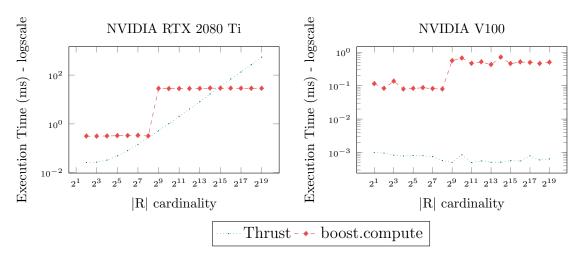

|   |      |        | 6.5.2.3 <b>Joins</b>                                          |       |

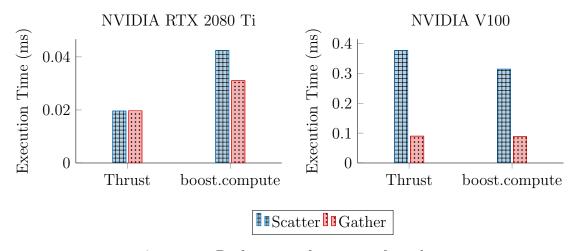

|   |      |        | 6.5.2.4 <b>Scatter &amp; Gather</b>                           | . 86  |

|   |      |        | 6.5.2.5 <b>Summary</b>                                        | . 86  |

|   |      | 6.5.3  | TPC-H Performance                                             | . 87  |

|   |      |        | 6.5.3.1 Single Library Performance                            | . 87  |

|   |      |        | 6.5.3.2 Cross Library Performance                             |       |

|   | 6.6  | Summ   | ary                                                           | . 90  |

| 7 | Tier | 2: Run | itime Layer - Developing an Execution Model                   | 93    |

|   | 7.1  | Introd | uction                                                        | . 93  |

|   | 7.2  | Relate | d Work                                                        | . 95  |

|   | 7.3  | Prelim | inaries on In-Memory Execution Models                         | . 96  |

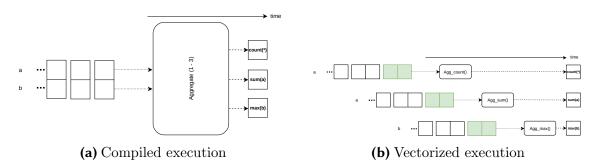

|   |      | 7.3.1  | Vectorized Execution                                          | . 96  |

|   |      | 7.3.2  | Compiled Execution                                            |       |

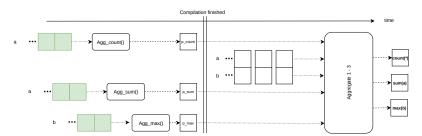

|   | 7.4  | Tether | : A Hybrid Query Execution Engine                             |       |

|   |      | 7.4.1  | Hiding Compilation Overhead With Vectorization                |       |

|   |      | 7.4.2  | Switching via Direct Aggregation                              |       |

|   |      | 7.4.3  | Switching via Hash Join                                       |       |

|   |      | 7.4.4  | Switching via Hash Aggregation                                |       |

|   | 7.5  | Experi | ments                                                         |       |

|   |      | 7.5.1  | Experimental Setup                                            |       |

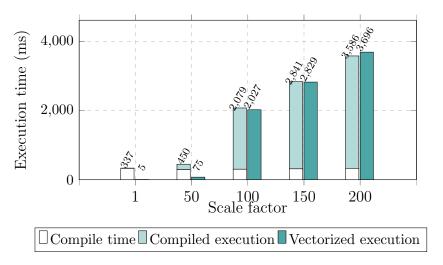

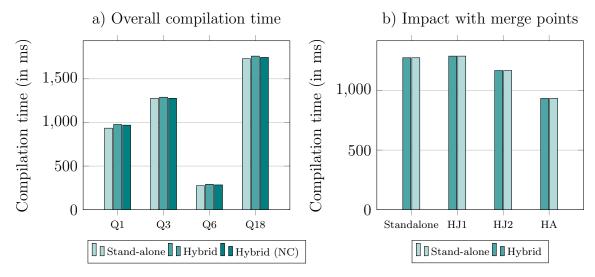

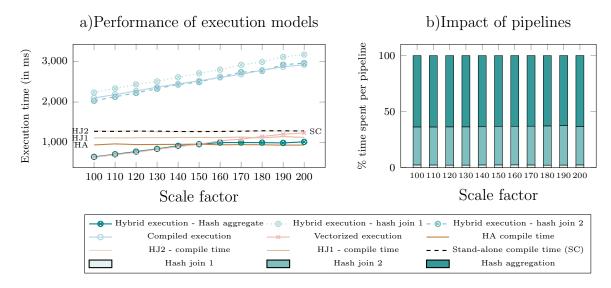

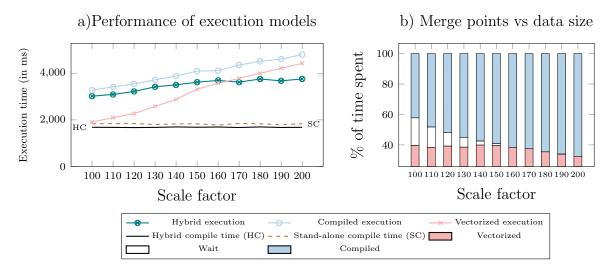

|   |      | 7.5.2  | Hybrid Compilation Overhead                                   |       |

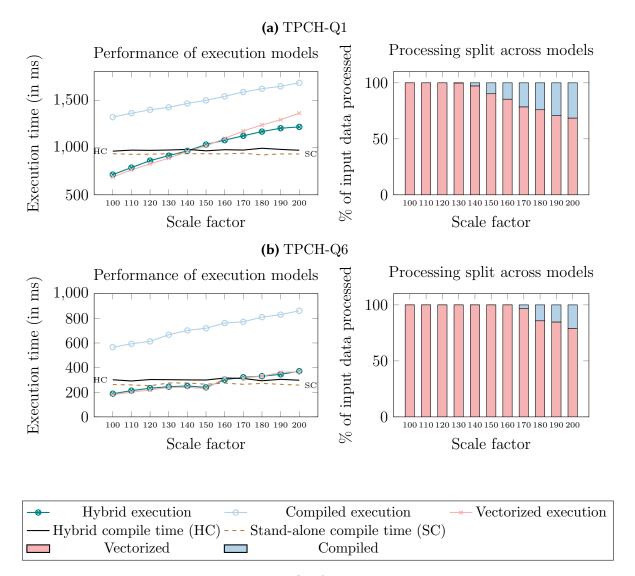

|   |      | 7.5.3  | Single-Pipeline Queries                                       |       |

|   |      | 7.5.4  | Informed Switching Points                                     |       |

|   | 7.6  | Discus | ssion                                                         |       |

|   | 7.7  |        | nary                                                          |       |

| _ |      |        | •                                                             |       |

| 8 |      |        | AMANT - A Pluggable Query Executor                            | 111   |

|   | 8.1  |        | Executor On Co-Processors - A Primer                          |       |

|   | 8.2  |        | d Work                                                        |       |

|   | 8.3  |        | ity in Programming Abstractions                               |       |

|   | 8.4  | -      | ry Executor to Plug-in Co-Processors                          |       |

|   |      | 8.4.1  | Device Layer                                                  |       |

|   |      |        | 8.4.1.1 Case Study - Integrating a GPU                        |       |

|   |      |        | 8.4.1.2 Integration of Other Co-Processors                    |       |

|   |      | 8.4.2  | Task Layer                                                    |       |

|   |      |        | 8.4.2.1 Task Model                                            |       |

|   |      |        | 8.4.2.2 Primitive Definitions                                 |       |

|   |      |        | 8.4.2.3 I/O Definitions                                       |       |

|   |      | 8.4.3  | Runtime Layer                                                 |       |

|   | 8.5  | Execut | tion Model Alternatives for Co-Processors                     |       |

|   |      | 8.5.1  | Limitations in Operator-At-A-Time Execution in Co-Processors  |       |

|   |      | 8.5.2  | Chunked Execution for Arbitrary Co-Processors                 | . 123 |

|   |      | 8.5.3  | Case Study: Pipelined Execution in GPUs for Concurrent Execu- |       |

|   |      |        | tion with Data Transfer                                       |       |

|   | 8.6  | Experi | ments                                                         | 127   |

| X |  |  | Contents |

|---|--|--|----------|

|   |  |  |          |

|     | 8.7   | 8.6.2<br>8.6.3 | Profiling Primitives                                | 129<br>130 |

|-----|-------|----------------|-----------------------------------------------------|------------|

| 9   | Con   | clusion        |                                                     | 135        |

| Α   | Арр   | endix          |                                                     | 141        |

|     | A.1   | Benchn         | nark Queries  .  .  .  .  .  .  .  .  .  .  .  .  . | 141        |

|     | A.2   | Code S         | nippets for Sort-Based Aggregation                  | 143        |

|     | A.3   | Tether -       | - Linking Vectorwise with Hyper                     | 145        |

| Bil | bliog | raphy          |                                                     | 147        |

# **List of Figures**

| 1.1  | Various realization of SIMD vectorization of hashing techniques showing impact over performance                                                                                             | 3  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Basic components in a GPU                                                                                                                                                                   | 11 |

| 2.2  | Basic components in a TPU                                                                                                                                                                   | 13 |

| 2.3  | Basic components in a MIC                                                                                                                                                                   | 14 |

| 2.4  | Basic components in an APU                                                                                                                                                                  | 14 |

| 2.5  | Basic architecture of an FPGA                                                                                                                                                               | 15 |

| 2.6  | Common paradigms for programming on a heterogeneous processors environment as given by Heimel et al                                                                                         | 18 |

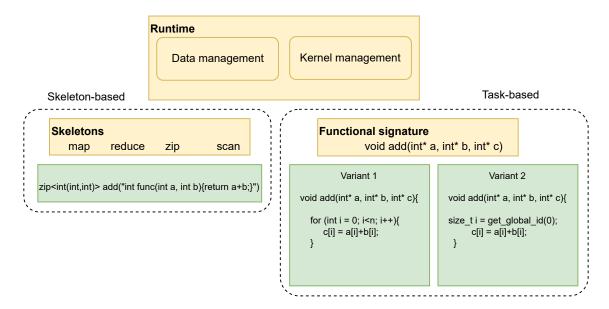

| 2.7  | Example of abstraction model paradigms. Modules in yellow are offered out-of-the-box and green are provided by developers                                                                   | 24 |

| 2.8  | Example of code generated using skeletons offered by HAWK                                                                                                                                   | 26 |

| 2.9  | Example of variant handling offered by elastic functions                                                                                                                                    | 28 |

| 2.10 | Possible cross-device optimization strategies using query execution plan of TPC-H Q6                                                                                                        | 31 |

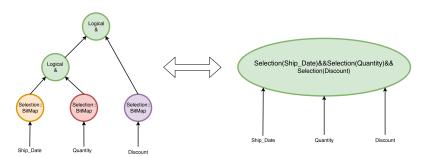

| 2.11 | Example of code fusion using multi-column predicates                                                                                                                                        | 32 |

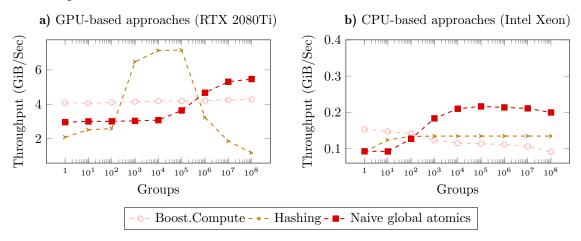

| 4.1  | Throughput of different group-by approaches on a RTX 2080 Ti GPU and Intel Xeon CPU on 2 <sup>27</sup> integers with uniform random distribution. Note, the different scales of the y-axis. | 44 |

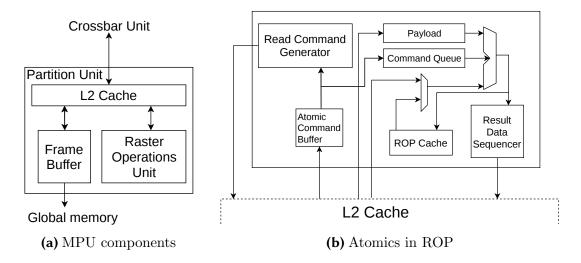

| 4.2  | Components involved in global memory atomics                                                                                                                                                | 47 |

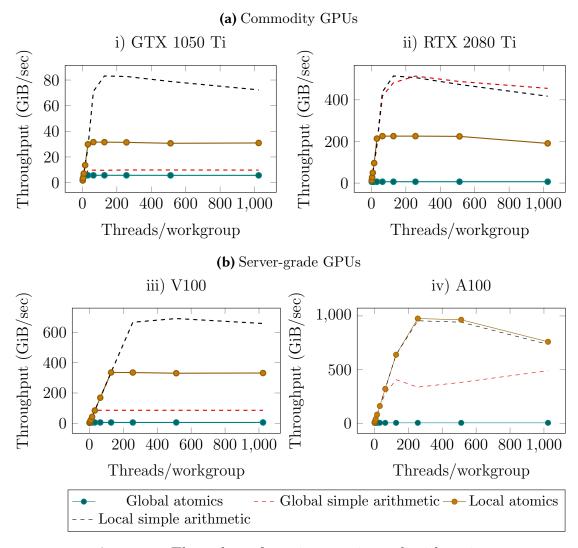

| 4.3  | Throughput for naive atomics and arithmetics                                                                                                                                                | 48 |

| 4.4  | Three-phases for parallel aggregation                                                                                                                                                       | 50 |

| 4.5  | Using private address space in GPU for storing partial aggregates                                                                                                                           | 51 |

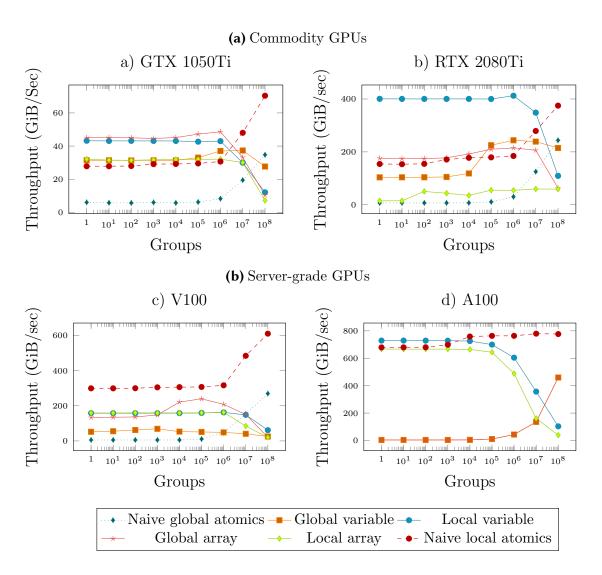

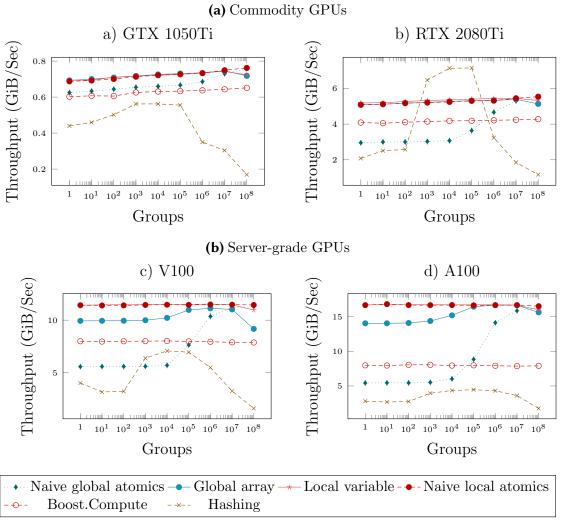

| 4.6  | Throughput profile varying with changes to group and thread size across different NVIDIA GPU generations                                                                                    | 53 |

| 4.7  | Impact of varying chunk and threads sizes over throughput                                                                                                                                   | 54 |

xii List of Figures

| 4.8  | Performance comparison of atomic variants                                                                                                                                      | 55 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Overall comparison against state-of-the-art competitors. The performance of atomic variants now includes sorting                                                               | 56 |

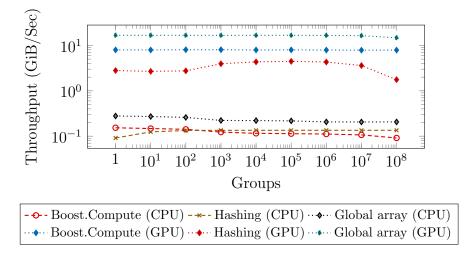

| 4.10 | Throughput comparison of grouped aggregation in CPU (Intel Xeon) and GPU (A100) $\dots$                                                                                        | 57 |

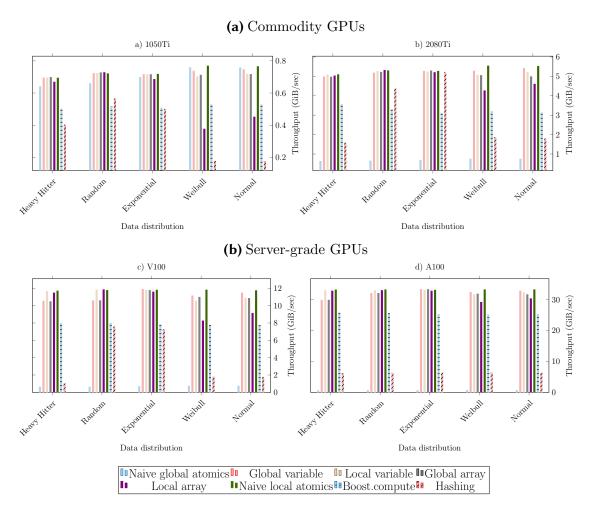

| 4.11 | Performance of aggregation techniques across various data distributions                                                                                                        | 58 |

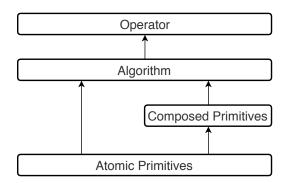

| 5.1  | Hierarchy in realizing primitives                                                                                                                                              | 62 |

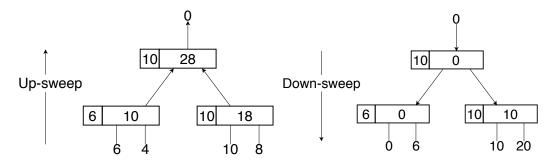

| 5.2  | Example of prefix-sum phases                                                                                                                                                   | 64 |

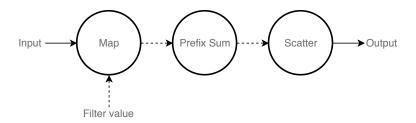

| 5.3  | Composing filter                                                                                                                                                               | 66 |

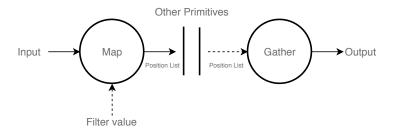

| 5.4  | Composing materialize                                                                                                                                                          | 68 |

| 5.5  | Composing hash build                                                                                                                                                           | 68 |

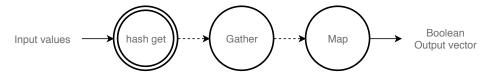

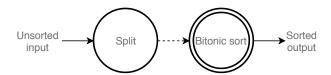

| 5.6  | Composing hash probe                                                                                                                                                           | 69 |

| 5.7  | Composing split                                                                                                                                                                | 69 |

| 5.8  | Composing sort                                                                                                                                                                 | 70 |

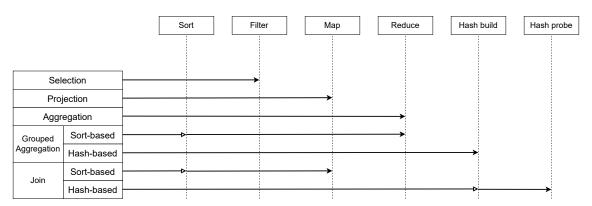

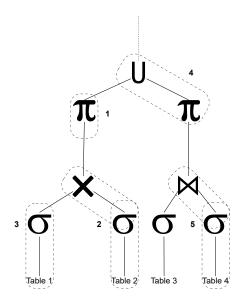

| 5.9  | Composing DBMS operators from primitives                                                                                                                                       | 71 |

| 5.10 | Different pipeline patterns                                                                                                                                                    | 72 |

| 6.1  | Hierarchy of abstraction levels characterizing languages, wrappers, and libraries for heterogeneous computing                                                                  | 77 |

| 6.2  | Proportion of GPU libraries. Left: proportion of libraries across various application domains. Right: Proportion of GPU libraries and their underlying implementation language | 80 |

| 6.3  | Adapter design pattern used for plugging libraries                                                                                                                             | 82 |

| 6.4  | Transfer times for different libraries                                                                                                                                         | 83 |

| 6.5  | Performance for selection with varying selectivity                                                                                                                             | 84 |

| 6.6  | Performance for Group-by with varying group sizes                                                                                                                              | 85 |

| 6.7  | Performance for join with varying R-table size                                                                                                                                 | 86 |

| 6.8  | Performance for scatter & gather                                                                                                                                               | 87 |

| 6.9  | Performance of TPC-H Queries                                                                                                                                                   | 88 |

| 6.10 | Performance of TPC-H queries using inter-library execution                                                                                                                     | 89 |

| 7.1  | Single threaded performance for TPC-H Q6 using vectorized and compiled-code execution                                                                                          | 94 |

| 7.2  | A sample hybrid query execution plan in <i>Tether</i> using TPCH Q3                                                                                                            | 97 |

List of Figures xiii

| 7.3  | Direct aggregation with execution models                                                                                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.4  | Hybrid aggregation                                                                                                                                                                                                         |

| 7.5  | Stand-alone vs. hybrid compilation time                                                                                                                                                                                    |

| 7.6  | Execution profile for single-pipeline queries                                                                                                                                                                              |

| 7.7  | Illustrating the impact of switching points using TPCH-Q3 106                                                                                                                                                              |

| 7.8  | Illustrating wait time while switching using TPCH-Q18 107                                                                                                                                                                  |

| 8.1  | A common pluggable executor for any type of SDK                                                                                                                                                                            |

| 8.2  | Architecture with a unified runtime and interfaces (purple blocks) to interact with plugged components                                                                                                                     |

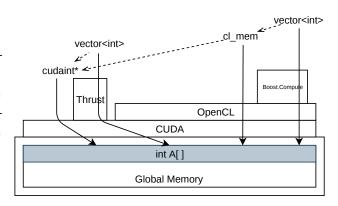

| 8.3  | Data types across SDKs. Data type (Solid) used by a developer & in SDKs (dotted)                                                                                                                                           |

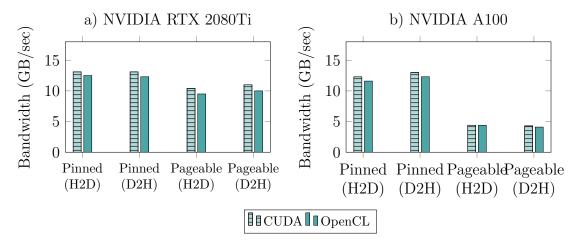

| 8.4  | Data transfer bandwidths using CUDA and OpenCL across GPUs. H2D: Host to device, D2H: Device to host                                                                                                                       |

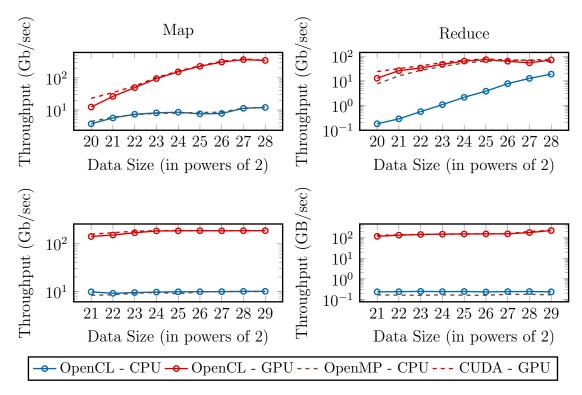

| 8.5  | Performance of map and reduce depends on the underlying implementation, as well as the device. (The results are measured on top: NVIDIA RTX 2080Ti and Intel core i7-8700 & bottom: NVIDIA A100 and Intel Xeon Gold 5220R) |

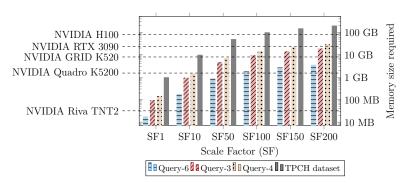

| 8.6  | Memory capacity in GPU devices vs memory required for processing TPCH data                                                                                                                                                 |

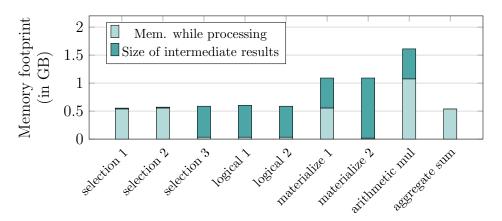

| 8.7  | Memory footprint of individual primitives in TPCH-Query 6 124                                                                                                                                                              |

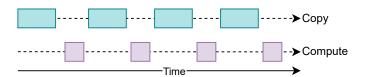

| 8.8  | Process flow in chunked execution model                                                                                                                                                                                    |

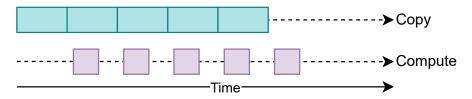

| 8.9  | Process flow in pipelined execution model                                                                                                                                                                                  |

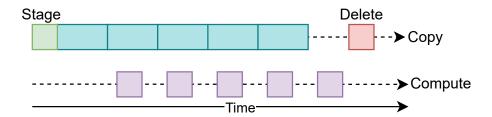

| 8.10 | Process flow in 4-phase pipelined execution model                                                                                                                                                                          |

| 8.11 | Dual memory spaces for concurrent transfer-execution                                                                                                                                                                       |

| 8.12 | Profile of primitives in OpenCL, OpenMP and CUDA                                                                                                                                                                           |

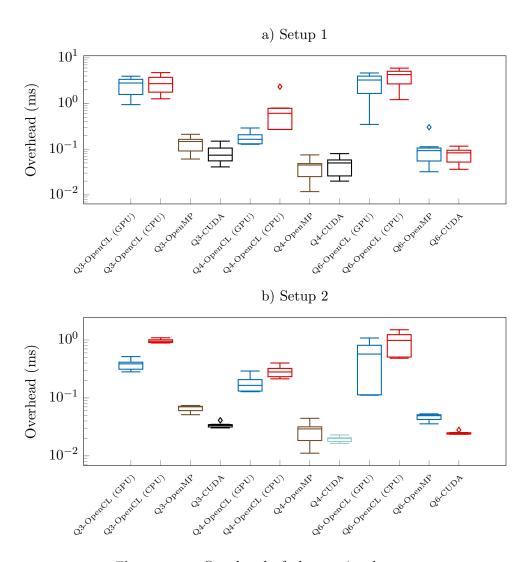

| 8.13 | Overhead of abstraction layers                                                                                                                                                                                             |

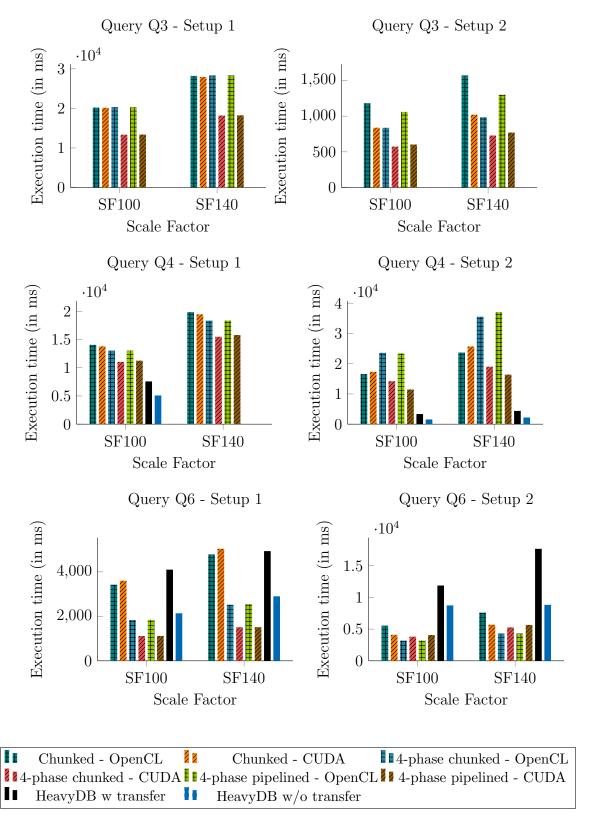

| 8.14 | Performance of the execution models versus HeavyDB across various scale factors                                                                                                                                            |

| 9.1  | An updated query engine for plugging in an arbitrary co-processor 137                                                                                                                                                      |

# **List of Tables**

| 3.1 | Common characteristics of skeleton-based systems                                   |

|-----|------------------------------------------------------------------------------------|

| 3.2 | Common characteristics of component-based systems                                  |

| 5.1 | Properties of atomic primitives                                                    |

| 6.1 | Libraries and their properties based on our survey                                 |

| 6.2 | Mapping of library functions to database operators 81                              |

| 8.1 | Primitive definitions for encapsulating multiple database operator implementations |

| 8.2 | Device setup used in evaluating ADAMANT engine                                     |

# Listings

| 2.1 | Simple parallel arithmetic using OpenMP         |

|-----|-------------------------------------------------|

| 2.2 | Creating memory space using OpenCL              |

| 2.3 | Simple parallel arithmetic kernel using OpenCL  |

| 2.4 | Spawning threads for kernel execution           |

| 2.5 | Allocating memory space using CUDA              |

| 2.6 | Simple parallel arithmetic kernel using CUDA    |

| 2.7 | Spawning threads using CUDA                     |

| 7.1 | Compiled hash probe                             |

| 7.2 | Hybrid hash probe                               |

| 8.1 | OpenCL code for transferring data to a GPU      |

| 8.2 | OpenCL code to allocate space in unified memory |

| 8.3 | OpenCL code to delete space                     |

| 8.4 | OpenCL code to compile a kernel                 |

| 8.5 | OpenCL code for kernel execution                |

# 1. Introduction

Today's co-processor landscape is broad and diverse, with numerous processors differing in their architectures, programming approaches, and processing capabilities, just to name a few. Such diversity in co-processors is necessary to fulfill the needs of many performance-hungry applications. Nowadays, these applications – Database Management Systems (DBMS) being one among them – running on a co-processor are often rewritten to utilize the processor's capabilities to match the performance needs. Such reworks are costly and require expert knowledge of both the hardware and the application. Hence, many researchers work on exploring ways to optimize an application to better fit a target co-processor.

#### **Co-Processor Accelerated DBMS**

The early 2000s saw increased use of GPUs (Graphical Processing Units) for query processing<sup>1</sup>: Ranging from offloading a few database operators [80] to a fully-fledged query processor [87, 91, 15]. A similar trend is seen currently with FPGAs (Field Programmable Gate Arrays), leading to research outcomes such as offloading operators [3], up to supporting fully-fledged queries [147]. Similarly, works are also undertaken to utilize other co-processors like APUs (Accelerated Processing Units), MICs (Many Integrated Cores), etc. Hence, many such works have already explored ways to use different co-processors for query execution [37, 154, 67]. Commonly, most of these works re-implement an existing query engine to run on its target co-processor. With new and diverse co-processors ready to hit the market on the horizon, we expect more query engines to be developed for these new ones as well. Such a trajectory will lead to varying implementation alternatives for a database operator across each of these co-processors. Hence, it is necessary to have a system that can manage these co-processor-implementation combinations to support any arbitrary co-processor.

Moreover, while exploring a new implementation for a database operator, one must invest time in developing and optimizing other co-processor driver code as well (like data management between host and co-processor). Such drivers, even though they

<sup>&</sup>lt;sup>1</sup>DBMS with GPU support: https://dbdb.io/browse?hardware-acceleration=gpu

2 1. Introduction

have no performance impact, are still necessary for execution. For example, to test kernel execution on a GPU, we must also implement the function to compile the kernel on the device. Thus, a query engine over a co-processor must also have these driver components integrated into it.

To sum up, a query engine over any co-processor is a tightly coupled mix of query execution components and co-processor components. Hence, we see diverse query engines tuned for each of the co-processors as they are developed, interspersing query engine code with co-processor code. However, such diversity meant that we had to rework a query processor from scratch for any new co-processor, which takes a considerable effort. Thus, even though many such co-processor-accelerated query engines exist, there is still a gap for a holistic query execution engine that can support any arbitrary co-processor.

In this work, we investigate a query engine that enables developers to plug in a co-processor without rebuilding a complete one. To avoid rework, we envision a layered architecture that separates device drivers from operator implementations so that we can reuse and modify the code without affecting other functionalities. Developing a co-processor-pluggable query engine comes with various challenges. To understand these, we must first study the implications of hardware awareness over DBMS and the current trends in co-processor acceleration.

#### 1.1 The Need for Hardware-Awareness in DBMS

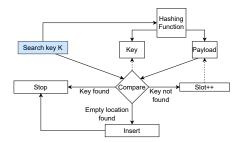

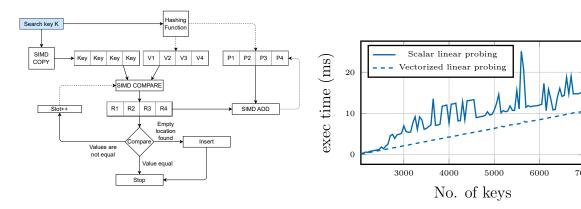

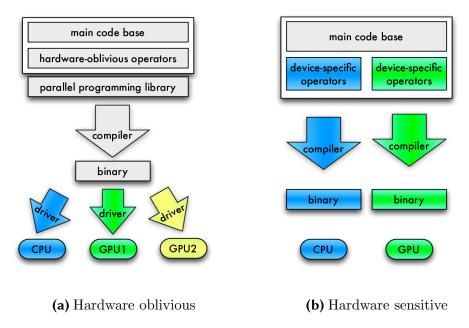

Owing to the growing data sizes, DBMS are made to be hardware-aware to ensure a reasonable query execution time. This includes placing the complete table in the main memory (popular example being MonetDB [29]), cache conscious data access [31], hardware sensitive database operators [41], etc. Specifically, with a hardware-aware DBMS operator, many researchers study the underlying processor architecture to come up with a more 'architecture-friendly' operator to gain additional benefits. For example, utilizing SIMD registers in modern CPUs has been shown to increase the performance of DBMS operators. To understand the benefit of hardware-awareness, let us consider the example of hashing: Linear probing is a simple hashing technique as the algorithm in Figure 1.1-a and its execution is visualized in Figure 1.1-b. As we can see, the scalar execution—begins by reading the search key (blue block), and hashing it to identify the target location. Based on the existing values in the target, we have three outcomes: 1) the key is already present—which leads to incrementing the key's count, 2) the slot is empty—insert the search key and 3) a different key is present—increment the slot and insert again. Such workflow in SIMD becomes fairly complicated. As Figure 1.1-c shows, the search key must be replicated to fit the SIMD vector lane. Next, the keys in the target location are fetched and compared with the target key. Based on resultant comparison masks (M1 until M4), we follow three possible outcomes as listed above. We can see from comparing Figure 1.1-b & c, that a complex execution flow is needed for a comparatively simpler function. Still, the outcome of such re-implementation shows additional performance benefits, such as in the case of Figure 1.1-c, where vectorized is nearly twice as fast as the scalar implementation. This is one of the alternative solutions for group-by-aggregation over SIMD. Similar solutions are also available for other operators over SIMD and other processor components, and even further—over other co-processors.

#### Algorithm 1: Linear probing

(a) Algorithm for simple linear probing

(b) Scalar workflow for linear probing

(c) SIMD workflow for linear probing

**(d)** Performance of vectorized linear probing with random distribution

**Figure 1.1:** Various realization of SIMD vectorization of hashing techniques showing impact over performance

However, developing such co-processor-aware solutions is not trivial. One needs to be an expert in the processor architecture to develop an operator implementation that utilizes the underlying device to its maximum extent. Even though developers are aware of the processor architecture, they must also know the instructions within the various SDKs available for the co-processor. This poses a challenge to developers as there are diverse co-processors, with each co-processor having diverse SDK support.

# 1.2 Challenges in Hardware & SDK Trends

Until recently, not many co-processors were present in the market to aid a host CPU. Similar is the SDK support for these co-processors to develop different applications. Only at the turn of the decade - 2010s - did we see a rise in different SDKs for each device. For example, previously, GPUs were mainly used for graphical applications. However, with the advent of GPGPUs (General-Purpose computing on Graphics Processing Units), other applications are also being supported over the device. Similarly, FPGA with its VHDL support is now one of the suitable devices to accelerate other applications, including DBMS.

1. Introduction

However, developing such a cross-device application needs considerable effort. Efforts in terms of understanding a co-processor architecture, as well as knowing the SDKs (Software Development Kits) operate on a particular component in the underlying architecture. For example, recent GPU architectures support parallel aggregation functions - commonly called *atomics* - directly through a hardware component (more in Chapter 4)<sup>2</sup>. One has to study these SDKs and their relation to the target architecture to utilize the device effectively. Moreover, SDKs provide a varying level of specialized access to hardware components. The access ranges from completely abstracting hardware-related components to specialized access to individual components (more in Chapter 5). One can develop a database operator from any of these levels of abstraction, resulting in various implementation alternatives for even a single database operator.

# 1.3 DBMS over Heterogeneous Co-Processors

To sum up, on the one hand, we see a strong argument favoring the need for hardware-aware query processing. On the other hand, we have growing diversity in hardware and SDKs, resulting in various query processor realizations. Therefore, there is a potential to develop a query processor over each co-processor and SDK combination. However, such an approach is time-consuming. Furthermore, these solutions must be combined to support an overall best-performing query processor.

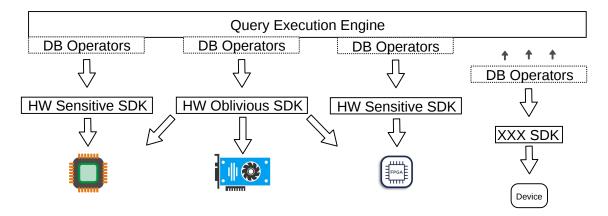

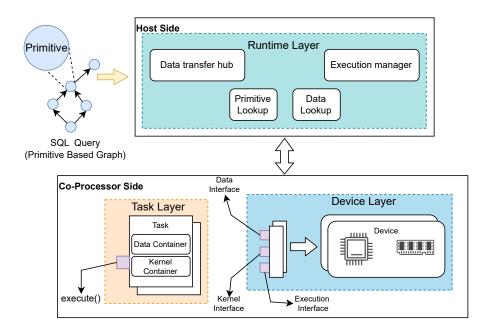

Hence, it is imperative to develop a query processor that reduces the implementation effort, providing DBMS support out-of-the-box for any abstract co-processor. To achieve such a holistic query processor, we need a system that supports plugging in a co-processor driver as well as its SDK implementation of DBMS operators. To this end, we explore in this thesis, the abstractions necessary to have such a pluggable architecture with a runtime supporting query execution out-of-the-box on the plugged device.

## 1.4 Goal of this Thesis

The ultimate goal of the thesis is to explore a query execution engine that supports plugging any arbitrary co-processor. Such a co-processor accelerated DBMS benefits from optimizations on co-processor drivers as well as database operator implementations. Therefore, an abstract pluggable query executor must also have interfaces that can be extended to add the above-mentioned two optimizations. In addition to the optimized code routines for the underlying co-processor, a query executor must also handle the query execution itself. Hence, it is imperative to explore a runtime that can handle query execution over any abstract co-processor. Thus, to achieve the goal of an abstract query executor, we must investigate three dimensions of the executor. Subsequently, we envision a three-tier architecture, with each addressing a particular challenge regarding pluggability.

<sup>&</sup>lt;sup>2</sup>These are available in NVIDIA CUDA SDK as atomic\_add()

**Tier-0/1**: Device layer - We explore the right level of abstraction for interfacing different co-processors.

**Tier 1**: Task layer - We explore the right level of abstraction for the database operators and realize them using the existing SDK.

**Tier 2**: Runtime layer - We explore ways to integrate pluggable interfaces into a common runtime. The runtime supports alternative execution models.

The first two layers explore ways to interface co-processor driver code and its corresponding DBMS operator implementations. Specifically, in the device layer, we focus on developing interfaces for data management that are integral for query execution. The task layer extends interfaces to include an operator implementation over the plugged-in co-processor. The runtime layer acts as the mediator between the query executor and our interfaces. We build our runtime layer using the interfaces designed above, therefore allowing us to have dynamic execution calls across various co-processors. The runtime takes in a query plan and handles execution of it across various co-processors.

# 1.5 Contributions: Three Tiers of a Pluggable Query Executor

Our pluggable architecture allows one to integrate co-processors without making any changes to the runtime. The architecture also enables one to encapsulate various alternative implementations of a single database operator using its task layer. A similar encapsulation of various SDKs is also possible via the device layer.

The detailed challenges and our proposed solutions for each of these layers are detailed below.

# Tier 0/1: The Case for Hardware Sensitivity

At the start of this thesis, we make the case for the need for hardware sensitivity. Here, we explore the performance impact of hardware-aware implementation, as well as the effort invested in developing such an implementation. To this end, we conduct a case study on developing a *GPU-aware* group by aggregation. Specifically, we study sorting-based group by aggregation and modify it for the underlying GPU.

As GPUs are data parallel executors, they need synchronization for aggregation. In the case study, we synchronize aggregates using atomics in GPUs. Atomics are specialized serialization instructions executed using a dedicated hardware component in GPUs. Therefore, these functions make our implementation hardware-sensitive. Additionally, the function also exhibits varying performance with multiple tuning parameters. We evaluate these parameters and study the impact of hardware awareness on overall execution. Our evaluation shows these parameters have a significant impact in improving the execution - in some cases, with speed-up execution of up to 2x the naive approaches. Overall, our case study establishes the need for hardware-aware operators and shows their sensitivity to performance.

6 1. Introduction

## Tier 1: Pluggable Tasks

Though our case study shows clear performance implications of hardware awareness, we also see that considerable effort and expertise are needed to implement such a hardware-aware operator. Furthermore, even though many researchers have come up with efficient implementations, most of them are ad-hoc solutions [45, 101, 127, 128]. Integrating these ad-hoc solutions needs additional effort. Thus, a single holistic query executor merging these solutions needs to tackle two key challenges:

- Managing implementations across various levels of granularity. For example, sorting can be an ad-hoc implementation, like merge-sort for GPU, or is composed of various smaller functions. For example, Bingshen He and others compose their sort operator using split, map, prefix-sum [87]. Such variations lead to implementations across different levels of granularity present under a single roof (more in Chapter 5).

- An implementation can be realized in various levels of SDK abstractions, such as device-SDK, common wrapper, or expert-written library (more in Chapter 6).

Apart from these main challenges, we also need to consider the varying data representations in each of these implementations. Further, we can also see that some of the operators reuse common operator implementations. Hence, to capture these implementation alternatives, we need a common definition for the operator that spreads across different levels of realizations. Therefore, we survey the existing models and come up with definitions for primitives. To the challenge of varying dimensions of realizations, we place these primitives in different hierarchy levels. Using these definitions and signatures, we can include different operator implementations under a single implementation umbrella. Finally, to test the versatility of our primitive definitions, we realize them using different GPU libraries. By doing so, we study the usability of our task layer as well as the libraries.

Overall, within this tier, we study database operators to come up with granular primitives that encapsulate alternative realizations and test them with existing GPU libraries.

## **Tier 2: Query Execution Runtime**

Once we have a holistic representation of primitives, we need a system that bundles these implementations across different devices. This also includes handling the device-related functionalities like data management, kernel execution, etc. as well as some DBMS-related components: like a proper execution model for the given query plan. For the former, we propose a device layer, which allows for plugging in any abstract co-processor. For the latter, we propose a runtime with alternative execution models. Since the execution model is one of the key components of a query executor, an efficient execution model improves the overall performance. Hence, we study the existing execution models for traditional CPUs, i.e. the vectorized and compiled execution models, and extend them to support co-processors.

Before we go ahead with establishing an execution model for co-processors, we first study the existing ones and their implications for the CPU. Since vectorized and compiled executions are the prominent execution models, we explore their advantages and disadvantages. Based on our study, we find that compilation suffers from compile time, which contributes to a significant startup delay. To improve on this, we propose a hybrid execution model that follows an interpreted execution while the remaining query is being compiled. Our evaluations show that using such an execution model improves the overall performance by around 2-3x the traditional ones.

Since not all co-processors support reasonable compilation time, we stick with interpretation-based execution. Furthermore, one of the major concerns for databases over co-processors is the limited memory space. Due to this, scaling data sizes might not fit the device completely, and they suffer from executing such big data sizes. To support such execution, we propose a chunked execution model with 3 alternatives: 1) chunked, 2) pipelined, and 3) 4-phased. All these execution models are run on the host CPU, handling execution on the target co-processor.

## **Putting All Together**

Thus, stacking these three layers together, we can have a co-processor pluggable query executor - **ADAMANT**. Since the query processor layers are loosely coupled, the functionalities within the layers can be freely substituted without any changes or awareness of other layers. Furthermore, we also evaluate the performance of using our execution models with GPU as a co-processor. Their performance against HeavyDB shows that we can support any arbitrary query, as they will not run out of memory space in the device. Overall, our ADAMANT query engine has a performance range from dropping up to 3x until gaining speed-up of up to 3x the HeavyDB.

To summarize, the contributions of this thesis are:

- Exploring the hardware-sensitive implementation of non-standard primitives

- A survey of existing database primitives that can be combined to execute complete database operators developing a standard for our primitives

- Exploring GPU library implementation for standard primitives

- A hybrid execution model for traditional CPU-based query execution

- A scalable execution model for abstract co-processor execution

- A query executor with pluggable interfaces for easy co-processor integration

# 1.6 Corresponding Publications

The content of this dissertation is an extension of several peer-reviewed publications across workshops, conferences and journals. The following publications are listed in the order they appear in this dissertation.

• B. Gurumurthy, D. Broneske, M. Schäler, T. Pionteck and G. Saake, "An Investigation of Atomic Synchronization for Sort-Based Group-By Aggregation on GPUs," IEEE 37th International Conference on Data Engineering Workshops (ICDEW), Chania, Greece, 48-53(2021).

8 1. Introduction

• B. Gurumurthy, D. Broneske, M. Schäler, T. Pionteck and G. Saake, "Novel insights on atomic synchronization for sort-based group-by on GPUs". Distributed Parallel Databases 41, 387–409(2023).

- B. Gurumurthy, D. Broneske, T. Drewes, T. Pionteck, G. Saake, "Cooking DBMS Operations using Granular Primitives". Datenbank-Spektrum: Vol. 18, No. 3. pp. 183-193(2018).

- H. K. H. Subramanian, B. Gurumurthy, G. C. Durand, D. Broneske and G. Saake, "Analysis of GPU-Libraries for Rapid Prototyping Database Operations: A look into library support for database operations," IEEE 37th International Conference on Data Engineering Workshops (ICDEW), Chania, Greece, 36-41(2021).

- H. K. H. Subramanian, B. Gurumurthy, G. C. Durand, D. Broneske and G. Saake, "Out-of-the-box library support for DBMS operations on GPUs". Distributed Parallel Databases 41, 489–509 (2023).

- B. Gurumurthy, I. Hajjar, D. Broneske, T. Pionteck, G. Saake, "When Vectorwise Meets Hyper, Pipeline Breakers Become the Moderator". In International Workshop on Accelerating Analytics and Data Management Systems Using Modern Processor and Storage Architectures (ADMS@VLDB),1-10 (2020).

- B. Gurumurthy, D. Broneske, G. C. Durand, T. Pionteck and G. Saake, "ADAMANT: A Query Executor with Plug-In Interfaces for Easy Co-processor Integration," IEEE 39th International Conference on Data Engineering (ICDE), Anaheim, CA, USA, 1153-1166(2023)

# 1.7 Outline of this Thesis

The thesis is structured as follows: The next chapter - Chapter 2 - gives an overview of the current state-of-the-art in hardware-accelerated DBMS. The chapter covers the different co-processors currently available, their SDK support, and the challenges in integrating DBMS over these co-processors. We follow these with the existing runtime systems that support heterogeneous co-processor execution in Chapter 3. Next, in Chapter 4 we elaborate on our case study on hardware-aware database operation. Here, we study the GPU-aware group-by-aggregation function to investigate its performance implications. Using the outcome of the case study, we survey the existing database operators and their granular functions in Chapter 5 and realize their implementations over GPU using libraries in Chapter 6. The remaining chapters explore the runtime for our query engine. Similar to our database primitives, we start with understanding the existing execution models from query engines. Based on our study, we developed a hybrid execution model for modern CPUs, which is detailed in Chapter 7. Finally, we put our concepts together into a co-processor pluggable query engine. The engine is detailed in Chapter 8. Finally, we conclude the thesis and postulate on the possible future work in Chapter 9.

# 2. Tier 0: Current Co-Processor Ecosystem

The consensus nowadays is that the CPU has reached its scaling limitations [160]. Yet, the performance demands from a CPU continue to increase, mainly due to the exploding data growth. [180] This is particularly challenging for a Database Management System (DBMS) as an end-user expects query results in a reasonable time. Hence, many DBMS researchers work on optimizing the query engine for the underlying hardware system (such as aligning memory layout, maximizing cache utilization, using in-memory databases, etc.) to have improved query execution. One of these explored solutions to speed up query processing is to use additional co-processors.

A co-processor is a specialized processor adjunct to a general-purpose CPU, mainly developed to accelerate a particular task or application. Even though a co-processor architecture is tailor-made for a target application, it can be used for other general-purpose computing as well. One can use these processors to execute a custom function – built using co-processor APIs. Currently, various APIs are available for an individual co-processor, each having its performance implications over execution. Hence, achieving optimal performance from a co-processor requires us to be aware of both the hardware architecture and the corresponding API that allows access to it.

Due to the variety of co-processors and their corresponding APIs, we can develop multiple implementation variants for a single database operator. Hence, to ease the development effort, we have varying support for programming co-processors ranging from programming paradigms to different systems to generate custom code for a co-processor. Though these systems ease the development effort, additional efforts are needed to handle multiple implementations. Such a handler is typically included within the runtime of the target application, which in our case is a query executor.

In a gist, a DBMS over a co-processor requires changes to its query execution runtime. Such integration opens up various challenges and opportunities for improvement in the query execution runtime. In this chapter, we start with an overview of different co-processor architectures and their ecosystem, which we use to later explore the challenges when integrating them into a DBMS. We use these fundamentals to build our abstract query executor in the subsequent chapters of this thesis.

#### **Downfall of CPU Performance**

Before the emergence of co-processors, the CPU has been the sole processor supporting any performance-hungry applications. As the performance requirements from applications increased, CPU capability scaled proportionally to support their needs. The CPU kept pace by cramming more components onto ICs (integrated circuits), whose count Gordan E. Moore has estimated to be doubling every 18 months [160]. However, as is the case with all exponential trends, after a certain limit, doubling components gives only a marginal performance benefit. There are several technological barriers to this behavior, with the most prominent being the power wall. Since simply doubling ICs would make them power-hungry, their power density has to be kept constant. Dennard observed that voltage and current should be proportional to the dimension of a transistor, which is termed Dennard scaling. Exploiting this behavior, shrinking transistors proportionally required less voltage and current, making the overall power density constant. This trend continued until recently when modern chips can no longer shrink the transistor sizes without current leaks<sup>3</sup>. Thus, with the end of Dennard scaling, ICs cannot pack more components without increasing the power density. Hereafter, CPUs were unable to utilize 100% of the transistors without compromising on power. To maintain a fixed power budget, CPUs started to intermittently cool down and run only on a partial transistor count. Thus, to keep up with the performance, multicore CPUs have been introduced.

Such a multicore solution came with the cost of managing parallelism across the cores. Furthermore, doubling CPU cores might not scale beyond a few hundred cores, as managing the cores and powering them will also become an overhead. Thus, scaling performance in a CPU has become more and more challenging.

One other alternative solution to flattening CPU performance is to develop a task-specific co-processor. The co-processor contains only the necessary hardware components for processing a specific application. These co-processors work in tandem with CPUs, where the CPU simply offloads the supported task to a co-processor.

## 2.1 Current Generation Co-Processors

A co-processor is loosely coupled with a host CPU, typically using a pluggable interface (most commonly via PCI-E). Any input to the co-processor is offloaded into a device's memory before its execution. Though such an execution routine is common across co-processors, they differ in their internal architecture. In this section, we give a brief overview of the commonly available co-processors and their internals.

<sup>&</sup>lt;sup>3</sup>The leak is dissipated as heat

#### **GPU**—**Graphics Processing Unit**

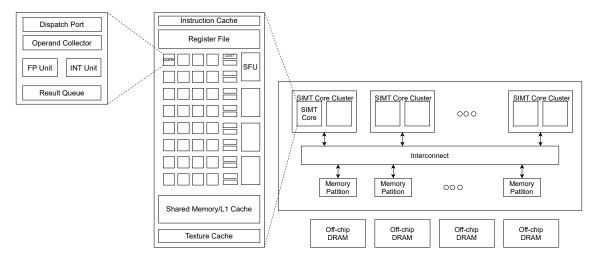

Video rendering is challenging for traditional CPUs, as thousands of pixels must be constantly updated in real time. Though updating a single pixel might be trivial, it gets fairly complex to update the millions of pixels present in modern displays within a reasonable time. To support such a growing pixel count, CPUs must be fast enough to avoid any significant delays. However, modern CPUs are ill-equipped for such a task. Hence, GPUs are deployed to update the pixel values concurrently. Accordingly, a GPU architecture is equipped with thousands of light-weight cores, each executing in a Single-Instruction Multiple-Threads (SIMT) fashion. These cores execute potentially thousands of threads among them, hence supporting massive data-parallel execution. Unlike CPUs designed to have fast response time, GPUs are designed to have high throughput. Hence, the architecture of a GPU also reflects this goal. The SIMT cores deliver high computation throughput while assisted by the faster interconnect that provides high memory bandwidth complete with various levels of caching.

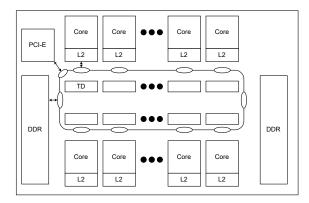

**Figure 2.1:** Basic components in a GPU

As Figure 2.1 shows, in an overview GPU has three main components: 1) off-chip memory—also known as global memory, which is the memory space for storing data from a host CPU, 2) crossbar—a data access component, that resolves the data access requests while execution, and 3) GPC or Graphics Processing Cluster—the processing core array. The GPC packs thousands of *lightweight* cores that work together in the data-parallel execution of an instruction. A set of GPU cores are clustered into SIMT clusters. The blocks on the top contain the cores. These are named *streaming multiprocessors* by NVIDIA and *compute units* by AMD. These cores share a common instruction cache as well as a data cache. This allows the device to reduce the overall latency within the system. Since numerous threads are working at any given instant, there will be lots of data access calls. These are resolved by an interconnect network (we explain this in detail in chapter 8). The interconnect links the cores with a dedicated off-chip memory in the device.

The single core of a GPC has a lower clock frequency as well as limited capability compared to a CPU core. For example, unlike a CPU, a GPU core is not equipped with branch predictors. It simply runs the else instructions following if instructions,

masking the non-qualifying threads in the corresponding branch. However, such small cores are packed together to support massive parallelism to provide extended performance. Further, memory accesses have high latency that needs to be hidden by processing. To this end, they spawn multiple threads for a given function and use context switching to hide the latency. This massive parallelism in GPUs well suits DBMS workloads. Hence, multiple works have investigated the use of GPUs for accelerating query execution (listed in Chapter 3). We extensively use a GPU to explore co-processor pluggability in this thesis. Hence, we give an in-depth understanding of a GPU and its architecture in this section.

GPUs execute their tasks using threads. The execution here is quite different from CPU threads. In a CPU, the threads are grouped by the core and are normally executed together. In the case of a GPU, a group of threads (defined as warps in CUDA) execute together, and there can be multiple warps in the system. Each warp executes a single instruction in a lockstep. Due to this, in case there is a divergence, threads in a single path are executed together and later the threads follow the alternative path. Hence, it is advised to avoid branching statements in the execution. One more feature of the warp is that threads within the warp have access to a shared local memory in the system.

The GPU supports coalesced access rather than sequential access when reading from global memory. This is again beneficial for the memory controller as the memory access triggered from a warp will be in bulk for all the threads as they are executing in a lock step.

Due to their architecture, GPUs have become the most popular co-processor to a CPU, such that almost all commercial PCs come with a GPU. These commodity-range GPUs, even as of 2023 – nearly a decade after it was first released, are aimed at supporting gaming systems<sup>4</sup>. This is closely followed by use cases in data centers and professional visualizations. There are several niche cases like automotive, healthcare, and logistics, where GPUs are also employed. Such versatility of the GPU is due to its architecture supporting massive data-parallel execution. Such a data-parallel execution is also suitable for the above-mentioned applications as well as many others, like HPC, machine learning, and even query execution in our case. Still, efficiently deploying query execution on GPUs is an ongoing topic and consequently, various GPU-based query executors are currently present and many are still in development. Some commonly known GPU-accelerated DBMS include CoGaDB [38], GPUDB [87], MapD [54] etc.

Though a GPU is also used for accelerating AI applications, its internal components are still not tuned for the application. Current generation GPUs try to support both graphics acceleration and AI using dedicated cores like Tensor cores from Nvidia [96]. However, there are still trade-offs necessary to support both domains. Hence, as a dedicated support for AI, TPU (Tensor Processing Unit) is developed.

## **TPU-Tensor Processing Unit**

Tensor Processing Units are flagship devices from Google for supporting neural network applications. One of the main reasons for exploring TPUs is that Google

$<sup>^4</sup>$ NVIDIA investor report from 2023: https://s201.q4cdn.com/141608511/files/doc\_presentations/2023/02/nvda-f4q23-investor-presentation-final.pdf

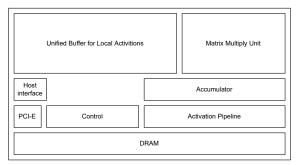

needed to double its data centers to work on machine learning workloads [185]. TPUs accelerate AI techniques (like deep neural network inferences), making them nearly 10x faster than their CPU and GPU counterparts. Similar to a GPU, the TPU contains the hardware components that are necessary for DNN (Deep Neural Network). Moreover, similar to a GPU, the TPU's instruction set also operates over a bulk of data [99].

A simplified block diagram for a TPU based on Jouppi et al. [100] is given in Figure 2.2. The bulk of the TPU space is allocated for the Matrix Multiply Unit. The unit contains 256×256 Multiple-Accumulators (MACs) capable of 8-bit multiplication followed by 16-bit accumulation, i.e., a MAC can process a 256-element sum per cycle.

Figure 2.2: Basic components in a TPU

The next biggest space is reserved for a Unified Buffer for Local Activations. It stores the intermediate results in a 24 MiB unified buffer. Finally, the unified buffer has a dedicated DMA to control data access from host memory.

At present, TPUs are exclusively used to speed up machine learning workloads. Specifically, the TPU is well-equipped to run CNNs (convolutional Neural Networks). Though a TPU better fits such AI workload, there is ongoing research to use them for accelerating query processing [93, 96].

Though a TPU fits the AI workload, it also suffers from missing out on many CPU features. Hence, different devices are developed to bridge this gap. Below are two of the most commonly available devices that contain all CPU features while supporting massive data parallelism in a GPU.

# **MIC-Many Integrated Cores**

MICs are the first of many core generations. Here, 10s of CPU cores are packed together to support massive parallel processing. MICs are mainly used in supercomputers and workstations. The first commercial MIC was Intel's Xeon Phi (code-named Knights Corner). it is capable of executing x86-compatible code out-of-the-box. In a nutshell, these are general-purpose CPUs put together to support high levels of parallelism. Unlike standard standalone CPUs, these are connected to a host CPU using PCI-E so that the host can offload some of its operations into the device.

In Figure 2.3, we depict the architecture of one of the MIC systems – Intel's Xeon Phi [170]. The architecture has: processing cores, caches, memory controllers, and a bidirectional ring interconnect. The cores are heavyweight, capable of processing complex operations, and even have a private L2 cache. They support in-order pipelines and up to 4 hardware threads, as well as SIMD vectorization. The whole MIC chip is cache coherent with MESIF<sup>5</sup> protocol [171].

<sup>&</sup>lt;sup>5</sup>derived from 5 protocol states: Modified, Exclusive, Shared, Invalid, and Forward

**Figure 2.3:** Basic components in a MIC

Due to the versatility of the cores in MICs, they are used for accelerating operations in a multitude of applications [125]. MICs are readily used in HPC [98], AI [151] and, naturally, in data processing [141, 161].

The main disadvantage of the MIC is again the managing of the complexity of parallelism. Specifically, communication becomes complex when more cores interact with each other, and complex data transfers take more time than processing using a single core. Hence, to partially solve this, APUs are introduced. These have both CPU and GPU in a single die.

#### **APU—Accelerated Processing Unit**

An APU, also known as an *iGPU* (short for integrated GPU) has both CPU and GPU in a single die, both accessing the same memory space (i.e., main memory). The main goal of such a fusion architecture (AMD names its APU platform as fusion architecture) is to have shared memory along with faster interconnects. Depending on the workload, the right device is selected. Usually, the CPU is suitable for serial workloads like web browsing, and cryptography, while the GPU han-

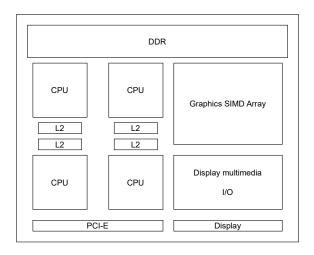

Figure 2.4: Basic components in an APU

dles data-intensive (vector processing favorable) workloads like real-time graphics rendering, data processing, etc. This avoids unnecessary data transfers and duplication (and subsequently no need for explicit coherency management, less energy consumption, and decreased latency). This also means we get fine-grained data sharing and a good spread of parallelism across both devices. In the next paragraphs, we give an overview of an APU architecture (focusing w.l.o.g on the AMD fusion architecture).

Figure 2.4 shows the recreation of AMD Fusion APU: Llano architecture [34]. As we can see in the figure, there are multiple CPU cores with their set of shared caches as well as the graphics accelerator on the same die. Since these two lie on the same die, they are connected to the memory (DDR3) using a high-speed bus. Some of the previous generation of APUs supported discrete address spaces for these two processors. Here, any data from the CPU has to be moved to the GPU addressable space for processing. Yet, this is supported by faster block transfers to copy data from one space to the other.

Since both the CPU and the GPU share a single memory space, data transfer is fairly easy compared to standalone GPUs. This leads to a fine-grained execution of an application across the processors. Hence, APUs are frequently researched for accelerating mathematical routines, video processing, and among others, database systems [90, 184] as well. Though the APU supports both CPU and GPU workloads because of its limited chip size, the performance of these devices in isolation is sub-par compared to the individual devices.

## FPGA-Field Programming Gate Arrays

Unlike the above devices, a Field Programming Gate Array (FPGA) supports synthesizing a custom digital circuit. Due to such a level of specialized implementation, FPGAs have gained popularity int he recent years as a suitable data processing device.

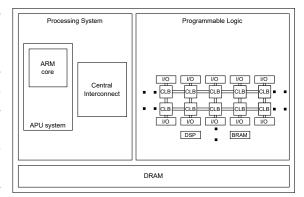

The architecture of an FPGA has two parts: Processor System (PS) and Programmable Logic (PL)<sup>6</sup>. The overview of the various components in an FPGA is given in Figure 2.5. The PS contains dual-core or single-core chips and its internal caches and other IO peripherals & interfaces. The PL part contains the Configurable Logic Blocks (CLB termed by Xilinx), routing resources, and IO for off-chip connections (commonly PCI-E to any possible interface). Additionally, the PL also contains DSP blocks and a small block RAM as well (of size 32 kB). Out of these, the key component in an FPGA is the CLB block, which can be configured to support any simple logic and storage functionality. These CLBs contain lookup tables (LUTs), through which one can ultimately design their custom circuit.

The next important feature of an FPGA is its routing architecture. Routing is responsible for feeding and fetching data bits across CLBs. They use wires and programming switches to route data bits across various CLBs. Putting these together, one can create any custom digital circuit leading to having a custom-built circuit for any software function, in our case any database operator. Overall, thousands of CLBs are present in a modern FPGA with a complex routing structure.

Due to such a large amount of configurable blocks available, we need a software stack to configure the device. A custom circuit in an FPGA can be built using a high-level Hardware Description Language (HDL) like VHDL (VHSIC—Very High-Speed Integrated Circuits program—Hardware Description Language). A synthesis tool (like Vivado) can use these VHDL descriptions to create a *netlist* of FPGA's configurable elements and their interconnections. Next, this netlist is mapped to the physical resources in the hardware.

Figure 2.5: Basic architecture of an FPGA

$<sup>^6\</sup>mathrm{As}$  per the architecture of Xilinx Zynq-7000: https://docs.xilinx.com/v/u/en-US/ds190-Zynq-7000-Overview

In between, various sophisticated functions like placement, routing, and bitstream generation are also carried out depending on the support of various synthesizers. Hence, to ease development, FPGAs are programmed either using RTL (Register Transfer Level) languages like VHDL, and Verilog or via HLS (High-Level Synthesis)—where the circuits are extracted, for example from C or OpenCL code. This provides a platform that can be tuned to perfection for any given domain-specific operation, providing higher throughput. Thus, FPGAs support a flexible and fully customizable architecture that can be adapted to suit any program. The device can be used to build custom data paths, bit-width, and memory hierarchies, making it a completely free environment.

One of the primary benefits of employing FPGAs lies in their ability to support high line rates while processing, making them well-suited for data processing. As a result, FPGAs are synthesized with queries featuring deeper pipelines to harness performance advantages [53]. Furthermore, this pipeline can be replicated to have data parallelism during execution. Finally, depending on the placement of the FPGA in the system architecture, one can use FPGA as [67]: 1) a dedicated co-processor: query or partial query pipeline is pushed to an FPGA for execution, 2) a bandwidth amplifier: FPGA sits between the data source (HDD) and the main processor (CPU). It does data compression/de-compression or filtering to ease data transfer bottleneck, and 3) a near data store: FPGA stores partial data values and performs in-situ query processing before initiating transfer the the main processor. Among these, with the latter two cases, FPGAs are mostly used to process data in-stream while processing and a query is spread across the CPU and co-processor. In this thesis, we focus on the former approach, where the FPGA is tagged as a co-processor via interconnects.

FPGAs are used in data processing to accelerate the execution of individual operators, to running complete queries. Additionally, FPGAs also act as a *near-data* processor that aids in pruning initial results within the data source, so that only a fraction of data is transferred to the main processor.

Nonetheless, a drawback of employing an FPGA is the intricate process of circuit synthesis, which can be exceedingly time-consuming and lead to a complex circuit design. Additionally, despite FPGAs supporting line-rate processing, they often operate at a lower clock rate compared to CPUs or GPUs and are typically enhanced with multiple execution pipelines.

#### **Other Devices**

In addition to those previously mentioned, there exist other accelerators, including smart NICs (Network Interface Controller) and digital signal processors that have heterogeneous architecture and support a particular workload. Further, there is an emerging trend of accelerating AI tasks using hardware accelerators like a Vision Processing Unit (VPU). Nonetheless, these devices currently offer support for specific use cases and have yet to undergo significant enhancements to function effectively as dedicated co-processors.

#### Interconnects

While discussing co-processors, it is also worthwhile to understand the various interconnects used for data movement between the co-processor and the host CPU.

Out of the various interconnects available, the most well-known one is the PCI Express (short for Peripheral Component Interconnect Express<sup>7</sup>). It is one of the most widely used interconnects that has a robust but considerable transfer rate difference across their versions (for example, PCI-E 3.0 has a transfer rate of 8.0 GT/s and PCI-E 4.0 has 16.0 GT/s). Other than the PCI-E, many device-specific connectors are also present. For example, nvlink from NVIDIA supports faster communication compared to the PCI-E (Their performance comparison is discussed in Chapter 8). Furthermore, there are other interconnects like HyperTransport [105], Infinity Fabric [118], Intel QuickPath Interconnect [193] etc. providing competing transfer rates.

Overall, in this section, we emphasized the diversity in co-processor architectures and their performance implications. We showed the various components that make up each of the co-processors, which are relevant for improving performance. However, we must use an appropriate API to program a co-processor to develop an efficient application.

# 2.2 Programming Co-Processors

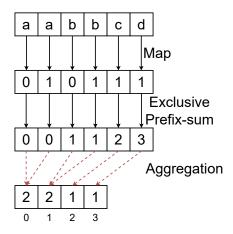

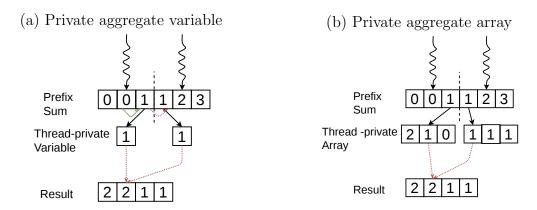

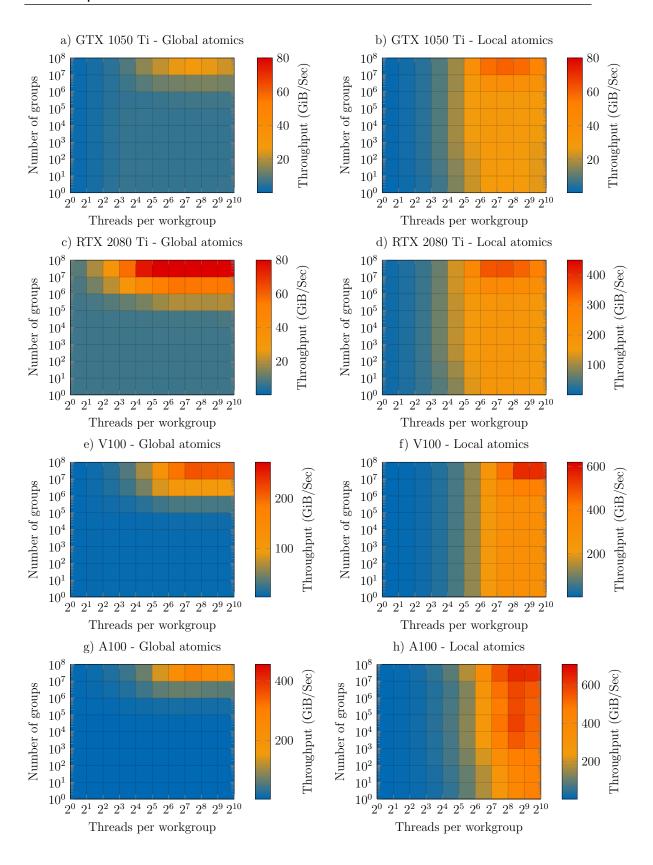

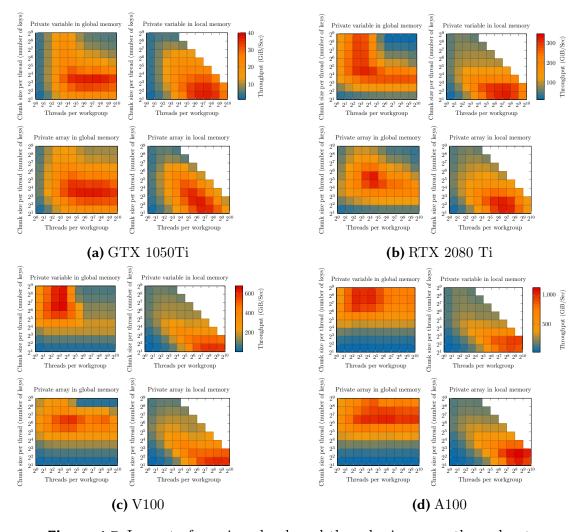

As we saw in the previous section, various internal components of a co-processor make up for its performance. A program puts to use these components efficiently to achieve maximal performance from a co-processor. This is enabled via various programming APIs and instruction sets (in virtual machines). In this section, we briefly present the API support for co-processors.