# **Epitaxial Semiconductor Nanostructure Growth with Templates**

#### **Dissertation**

zur Erlangung des akademischen Grades doctor rerum naturalium (Dr. rer. Nat.) vorgelegt der

Mathematisch-Naturwissenschaftlich-Technischen Fakult ät (mathematisch-naturwissenschaftlicher Bereich) der Martin-Luther-Universit ät Halle-Wittenberg

## von Herrn Zhang Zhang

geb. am: 31 January 1982 in Henan, China

#### Gutachterin/Gutachter:

- 1. Prof. Dr. Ralf Wehrspohn

- 2. Prof. Dr. Fan Hongjin

- 3. Dr. Walter Riess

Halle (Saale), den 29.06.2010

verteidigt am 17.12.2010

## **Preface**

Today, the prefix "nano" is not merely a unit of measure, but used widely in physics, chemistry, biology, and material science. Since the last two decades, nanoscience & nanotechnology have experienced a quick development. Named as nanotechnology, it mainly deals with science and technology on the nanoscale, utilization of nanomaterials for newer systems and devices. It is a field of applied science and technology whose primary theme is how to deal with the matter in the scale of nanometers, i.e. an extension of existing science & technology into the nanoscale, normally 1 to 100 nanometers. Generally, a nanomaterial is classified, according to its dimensionality, as zero-dimensional (nanoparticle), one-dimensional (nanowire & nanotube), or two-dimensional (thin film). Especially the zero- and one-dimensional nanomaterials possess low-dimensional structures which behave quite differently from their bulk counterpart. Scientists try to understand the fundamentals governing the nanomaterials, and develop theories related to the novel phenomena arising in these small structures. Design, fabrication, and integration of the systems and devices related to nanotechnology are transfered into industry.

In this thesis, several aspects regarding the controlled growth of semiconductor nanostructures with the assistance of several templates are illuminated. Chapter 1 gives a general introduction into the synthesis of one dimensional (1-D) semiconductor nanostructures. After a detailed description of the experimental setup, synthesis of Anodized Aluminium Oxide (AAO) which is one of the most important templates with controllable porous structure is the emphasis of Chapter 2. Given the requirement of Si integration and structural control, the methods presented here are devoted to the integration of AAO membranes with Si substrates. Several issues, such as the bottom anodization, barrier layer removal, and bonding, are crucial and determine the epitaxial growth starting from the interfaces. As an exception from the approach of growing nanowires, in the subchapter 2.5, the metal-assisted chemical etching of Si utilizing AAO templates is presented. In this case the nanowires are produced starting from a Si single crystal and remain after selective etching. Solving the problem of dependence of the etching direction on several parameters, the interconnected metal film synthesized utilizing AAO has the capability of realizing ordered Si nanowire arrays vertically aligned on all kinds of Si substrates. Afterwards, the AAO membranes, either free-standing or integrated with Si substrate, are used as growth template for Si and Ge/Si nanowires in Chapter 3. Several aspects of the standard vapor-liquid-solid (VLS) epitaxial growth mechanism are reconsidered, based on the analysis of Au-catalyzed Si isotope nanowire growth. An interpretation for the sharp Ge/Si heteroepitaxial nanowire interface is given in terms of a vapor-solid-solid (VSS) growth model for the Ge epitaxy inside AAO template. Chapter 4 is focused on a new technique which combines AAO both as imprint mask and growth template for the semiconductor nanowire epitaxy. Through the imprint process, a metal film could be repositioned at each pore bottom working as catalytic nanoparticle. Different catalytic metals as well as growth materials were investigated using this method.

Other templates assisting nanowire growth will be subjects of the last two chapters, with emphasis to further diameter shrinkage and diverse epitaxial structures. In the beginning of Chapter 5, bio-templated Au nanoparticles will be demonstrated as a substitute catalyst for positioning of sub-10 nm diameter Si nanowires. Subsequently, Si substrates with surface decoration are presented to control the epitaxial growth of sub-10 nm Si nanowire arrays. Based on high resolution TEM images of the growth interfaces, a model for the dependence of epitaxial growth direction of Si nanowires on the orientation of Si substrates is derived. The size-dependence of the sub-10 nm Si nanowire growth rate is related to different nucleation behaviours. Chapter 6 deals with size-control in the sub-10 nm regime with III-V materials, still using the surface-templated conception. Diverse heteroepitaxial nanowire structures together with sub-10 nm diameter control and the new catalyst Ag are presented. The feasibility of Si-integrated photoelectric device application is demonstrated by an optical characterization of both the photoluminescence and the emission life-time with these nanostructure arrays.

# **Contents**

| Pı | reface                                                                           | i  |

|----|----------------------------------------------------------------------------------|----|

| 1  | General Introduction                                                             | 1  |

|    | 1.1 Semiconductor Nanowire Growth                                                | 1  |

|    | 1.2 Controllable Epitaxial Nanostructures                                        | 4  |

|    | 1.3 Heteroepitaxial Nanowire Growth and Crystalline Structure                    | 6  |

|    | 1.4 Impurities & Defects                                                         | 8  |

| 2  | Anodic Aluminium Oxide (AAO) Combined with Si Growth                             | 11 |

|    | 2.1 Introduction                                                                 | 11 |

|    | 2.2 Experimental Setup                                                           | 13 |

|    | 2.3 AAO Growth on Si                                                             | 15 |

|    | 2.4 AAO Bonding onto Si                                                          | 17 |

|    | 2.5 AAO-Metal-Assisted Chemical Etching                                          | 20 |

|    | 2.6 Conclusions                                                                  | 22 |

| 3  | Epitaxial Growth of Semiconductor Nanowires                                      | 24 |

|    | 3.1 Silicon Nanowire Epitaxy in Free Space                                       | 24 |

|    | 3.1.1 Introduction                                                               | 24 |

|    | 3.1.2 Epitaxy of Isotopically Enriched Silicon Nanowires                         | 26 |

|    | 3.2 Si Growth with AAO Template                                                  | 30 |

|    | 3.2.1 Nonepitaxial Si Nanowire Growth                                            | 30 |

|    | 3.2.2 Synthesis of Polycrystalline Si Nanotubes                                  | 33 |

|    | 3.2.3 Epitaxial Si Nanowire Growth                                               | 37 |

|    | 3.3 Ge/Si Wire-on-Wire Heteroepitaxial Growth                                    | 38 |

|    | 3.3.1 Growth Mechanism                                                           | 39 |

|    | 3.3.2 Results and Discussions                                                    | 40 |

|    | 3.4 Conclusions                                                                  | 42 |

| 4  | <b>Epitaxial Growth of Semiconductor Nanowire Arrays with Structural Control</b> | 44 |

|    | 4.1 Introduction                                                                 | 44 |

|    | 4.2 Bottom-Imprint (BI) Method                                                   | 45 |

|    | 4.2.1 What is Bottom Imprint?                                                    | 45 |

|    | 4.2.2 BI for Au-catalyzed Si Nanowire Arrays                                     | 46 |

|    | 4.2.3 BI for InP Nanowire Arrays                        | 49  |

|----|---------------------------------------------------------|-----|

|    | 4.3 BI with Al as Catalyst                              | 51  |

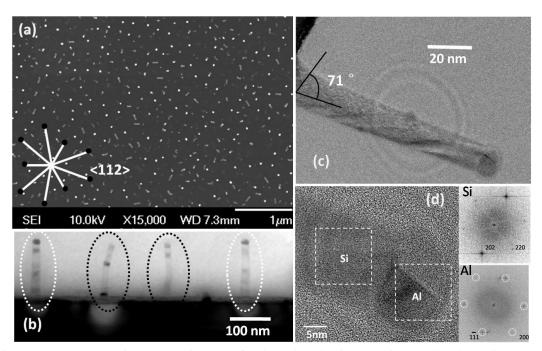

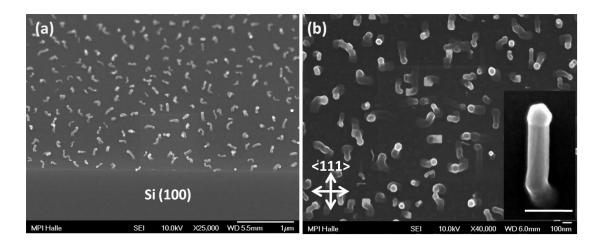

|    | 4.3.1 Al-catalyzed Si Nanowire VSS Growth in Free Space | 51  |

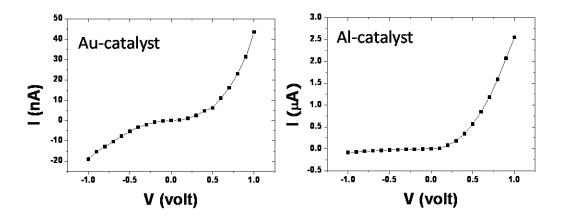

|    | 4.3.2 Electrical Characterization of Si Nanowires       | 53  |

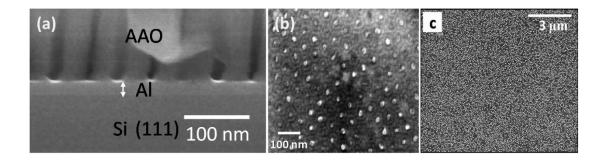

|    | 4.3.3 Al-catalyzed Nanowire Growth in AAO Template      | 54  |

|    | 4.4 Conclusions                                         | 58  |

| 5  | Templated Sub-10 nm Si Nanowire Epitaxy                 | 60  |

|    | 5.1 Introduction                                        | 60  |

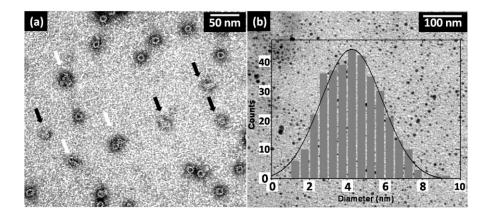

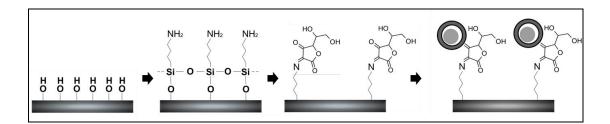

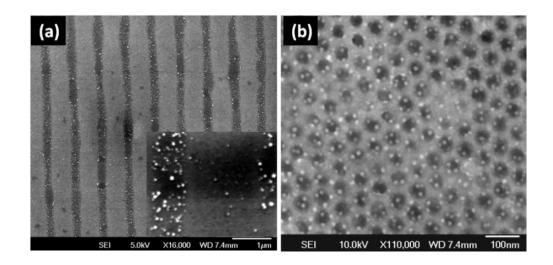

|    | 5.2 Apo-ferritin as Bio-template for Si Nanowire Growth | 61  |

|    | 5.2.1 Integration of Au-apoferritin on Si Substrate     | 61  |

|    | 5.2.2 Au-apoferritin-catalyst Si Nanowire Growth        | 64  |

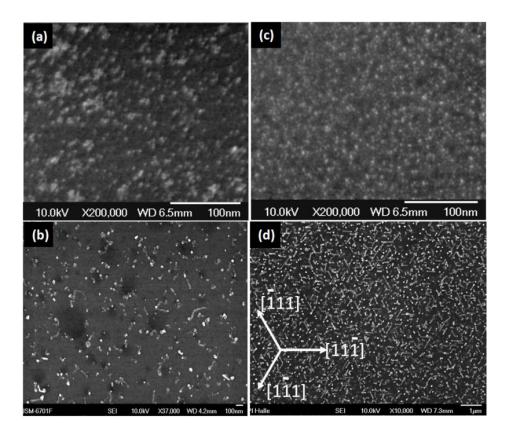

|    | 5.3 Surface Template for Sub-10 nm Si Nanowire Epitaxy  | 66  |

|    | 5.3.1 Synthesis of Sub-5 nm Au Nanoclusters             | 66  |

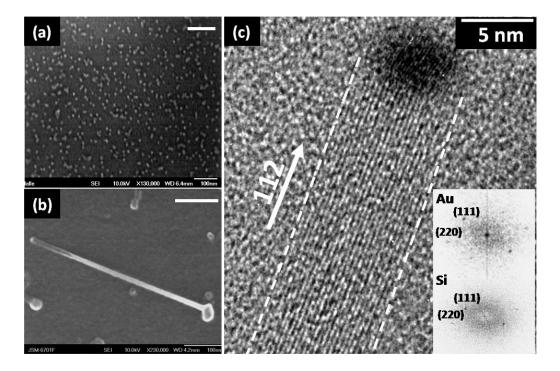

|    | 5.3.2 Sub-10 nm Si Nanowire Epitaxy on Si(111)          | 67  |

|    | 5.3.3 Sub-10 nm Si Nanowire Epitaxy on Si(110)          | 71  |

|    | 5.4 Conclusions                                         | 75  |

| 6  | III-V Nanowire Heteroepitaxial Growth on Si             | 76  |

|    | 6.1 Introduction                                        | 76  |

|    | 6.2 UHV-CBE Growth of GaP Nanowires on Si               | 77  |

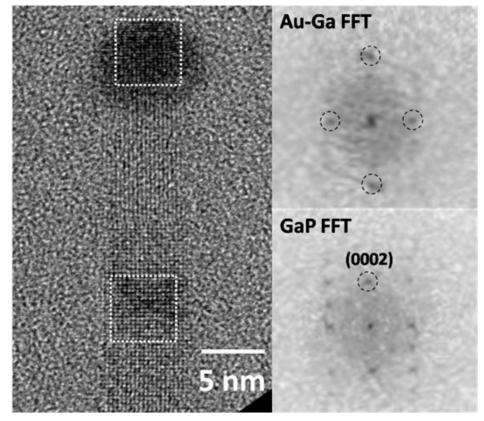

|    | 6.2.1 Au-catalyst GaP/Si Nanowire Heterostructures      | 78  |

|    | 6.2.2 Phase Transition in Sub-10 nm GaP Nanowire        | 82  |

|    | 6.2.3 Optical Characterizations                         | 88  |

|    | 6.3 Non-gold Catalyst Heteroepitaxy on Si               | 90  |

|    | 6.3.1 Al as a catalyst                                  | 91  |

|    | 6.3.2 Ag as a catalyst                                  | 93  |

|    | 6.4 Conclusions                                         | 97  |

| St | ummary                                                  | 98  |

| Bi | ibliography                                             | 101 |

| Aj | ppendix                                                 | 118 |

| A  | cknowledgement                                          | 128 |

## Chapter 1

#### **General Introduction**

During the last half century, low-dimensional structures dominated the modern semiconductor technology. The rapid developments of their products drive the dramatic downscaling of electronics, a miniaturization that the industry expects to continue for at least another two decades. Since the 1970s, the field-effect transistor (FET) became the fundamental logic element in semiconductor chips [Isa00]. Moore's Law states that the number of transistors on a given chip area doubles roughly every 18 months. Most of the functional semiconductor nanostructures are based on the Si platform at the present. Highly-controllable epitaxial growth methods such as molecular-beam epitaxy (MBE) and chemical-beam epitaxy (CBE) enable the precise control of composition and doping in the nanoscale. Although III-V compound semiconductors have been considered as building blocks for high speed and high frequency electronic devices [Kuz03, Gio07], recently, Si/Ge and Si/SiGe heteroepitaxial nanostructures have attracted much attention [Moo00, Dam04]. Low-dimensional nanostructures are promising for new, emerging semiconductor devices. Development of new methods for the down-scaling of homoepitaxial and heteroepitaxial semiconductor nanowires is indispensable for future nanoelectronics. Compositionally sharp hetero-interfaces in grown nanowires would allow to use quantum effects for devices. The key factor for the production of compositionally sharp Si-Ge hetero-interface is a low solubility of the elements Si and Ge in the catalyst. In contrast to the widely used vapor-liquid-solid (VLS) growth mechanism with a high solubility of Si and Ge in the liquid Si-Ge-Au catalyst, the vapor-solid-solid (VSS) growth mechanism offers a low solubility of Si and Ge in the solid Au-based catalyst. Generally, nanowire structures offer more prospects for defect free heteroepitaxial growth, with diameter control down to 10 nm (the requirement of post-CMOS), especially in material systems with big lattice mismatch [K 3504].

#### 1.1 Semiconductor Nanowire Growth

A semiconductor nanowire is generally a solid rod with a diameter less than 100 nm, which is composed of one or several semiconductor materials. A lower limit of a few nm in diameter was defined from a technological point of view [Xia03]. Experimentally, many techniques for the control of composition, doping, and the interface definition along the one-dimensional nanostructure have been developed, such as MBE, CBE, chemical-vapor epitaxy (CVD), and vapor-phase epitaxy (VPE) [Bar01]. The "growth" here means that the semiconductor nanowires are nucleated from precursors, no matter if in vapor or in liquid phase. Particularly, the growth is catalyzed by a metal particle, which strongly accelerates the growth rate and determines the diameter. Wagner and Ellis presented a model on the growth of silicon whiskers, which is generally described as the vapor-liquid-solid (VLS) growth mechanism [Wag65]. With several

metal catalysts, most of the semiconductor nanowires (Si, Ge, III-V compounds) have been synthesized via VLS growth [Giv87]. The target semiconductor materials should exhibit a binary-phase eutectic alloy with the catalyst at the growth temperature. The related crystal growth rate, in one dimension confined by the catalytic particle, is greatly enhanced resulting in the 1-D structure. The catalyst particle can also be a solid at growth temperature, the mechanism is then called VSS (vapor-solid-solid) [Sch09]. In general, there are two kinds of solid catalysts, compounds or metals. For Si this can be a silicide [Kam00] or a metal with high eutectic temperature [Wit10]. Otherwise, semiconductor nanowires can be grown catalyst-free, i.e. without any metallic catalyst involved, such as the Si and Ge nanowire growth with the decomposition of the corresponding oxide [Kim09], or the selective III-V nanowire growth by masking a substrate [Nob05].

It is forecasted that, by the end of the next decade, it will be necessary to augment the capabilities of the complementary metal-oxide semiconductor (CMOS) process by introducing multiple new devices. Such an attempt will hopefully realize some properties beyond the ones of CMOS devices. However, it is believed that, most likely, these new devices will not have all the properties of CMOS devices. Therefore, although silicon based technology will remain the mainstream semiconductor technology, it is anticipated that heterogeneous integration, either at the chip level or at the package level, will integrate these new capabilities around a CMOS core [Ard02]. 1-D nanostructures, such as semiconductor nanowires and carbon nanotubes, are explicitly mentioned as realistic additions. Among the potential feasibilities, researchers have focused a lot of efforts on studies of nanowire-based vertical surround-gate field-effect transistors (VS-FET) [Ng04]. The generic process for fabrication of a wrap-gated VS-FET could also be based on epitaxially grown Si nanowires [Sch06] and InAs nanowires [Bry06]. The advancement of doping techniques and high-quality heterostructures together with the simulation works of bandgap engineering to tuning the properties of FETs are quite promising [App08, Ver08]. Si nanowire-based solutions have been proposed in literature for optoelectronic devices [Tia07], biosensors [Cui01], and energy sources [Cha08], not mentioning other functional semiconductor materials.

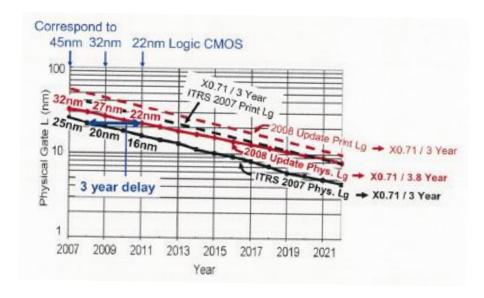

The roadmap for downscaling and introducing new technologies in the semiconductor industry from the International Technology Roadmap for Semiconductors (ITRS) 2008-update has summarized, that all of these improvement trends, sometimes called "scaling" trends are well laid out for the next ten years [Htt08]. As shown in Figure 1.1, although compared with ITRS 2007, the predicted trend has been amended to be less aggressive. The delay of gate-length shrinkage of logic CMOS is 3 years in near future, even 5 years in the middle term [Iwa09]. At the time of writing, devices based on semiconductor nanowires are, however, still in an embryonic stage from an industrial point of view. Their introduction as new technologies would require a long-term research and development (R&D) process in the electronics industry. Whether they will really have an impact on future post-CMOS technology which requires nanostructures smaller than 10 nm, depends on other factors like the intensive exploration of alternative materials, such as GaAs or InAs instead of Si. Controllable size and crystallographic orientation of semiconductor nanowires with high reproducibility is, therefore, one of the key issues on potential applications. In this thesis, the template-assisted growth of semiconductor nanowires will be demonstrated as

one promising solution, which could provide size controlled nanostructures while also enabling selective crystallization within the limited space.

Figure 1.1 Comparison of International Technology Roadmap for Semiconductors (ITRS) Overall Roadmap Technology Characteristics (ORTC) trends of printed (resist) and physical gate length to illustrate the "scaling" trends in near future [Iwa09].

In order to control the parameters such as nanowire positioning, growth direction, diameter, and catalytic material, an innovative bottom-up approach for fabrication and integration of semiconductor nanowires compatible with conventional Si technology will be the subject of Chapter 4. The specific target was to realize vertically aligned epitaxial Si<100> nanowires on Si (100) substrate with diameter less than 22 nm, together with ordered spacing. Moreover, the diameter size distribution has to be as small as possible. Before introducing this topic, an understanding of the fundamental issues related to material growth inside porous templates is of great importance. In particular, the metal catalysts commonly used for VLS growth, such as Au, must be integrated within the template properly. Chapter 2 will discuss the growth inside AAO (anodic aluminum oxide) templates, the conditions under which one-dimensional nanostructure preferentially form, and how the various structures can be used for integration with Si. The thermodynamic model for the size limitation of Au-catalyzed Si nanowire epitaxial growth pointed out by Tan et al. [Tan04], will be compared to experiment in Chapter 5. An extension of a bio-nanoprocess in order to break through the size barrier of post-CMOS devices is presented, through the use of bio-template with effective Au encapsulation with diameter below 5 nm. Complementary to the bottom-up growth, an improved method based on metal-assisted etching of Si, demonstrated the potential for the fabrication of vertically aligned sub-10 nm Si nanowires [Hua08].

The semiconductor nanowires discussed in this dissertation were grown by the use of vapor deposition synthesis techniques, i.e. ultra-high vacuum- (UHV-) CVD for Si, Ge, and III-V compounds growth. Semiconductor nanowire heterostructures can be realized through the growth on a desired hetero-substrate, or by adjusting the composition of gaseous precursors during growth. Compared with the two bulk materials, stress caused by a lattice mismatch could be relaxed

through the elastic deformation near the nanowire interface [Bak08], without introducing dislocations that detrimentally influence its physical properties. Axial heterostructures, along the nanowire growth direction, can be achieved using normal semiconductor nanowire growth techniques, i.e. the metal particle-catalyzed growth mechanism [Bj č02]. From an application point of view involving semiconductor nanowires for FET devices, the band gap can be tuned locally along the length of a Si nanowire, by introducing a segment of germanium with a sharp Ge/Si interface [Ver08]. Such techniques give access to completely new alternatives for device optimization, by the formation of tunnel barriers and quantum confined structures. The growth of a Ge/Si axial heterostructure will be the topic of Chapter 3. Ge nanowires also have promising electrical characteristics due to the high hole mobility of Ge compared to Si [Rod72]. In addition, a Ge/Si buffer structure on a Si substrate would be interesting for the integration of III-V semiconductor nanowire lasers with Si-based logic circuits. Due to the special one-dimensional character of nanowires, a Ge/Si buffer structure could work as a relaxed buffer layer for the growth of InGaAs/GaAs on Si substrate, without introducing dislocations, if the nanowire diameter is below the critical radius [K ä04].

## 1.2 Controlled Epitaxial Nanostructures

Epitaxial growth refers to a method of crystal formation on an underlying crystalline substrate. Semiconductor epitaxy can be realized from gaseous or liquid precursors. With the substrate surface intrinsically serving as a seed crystal, or by a surface modification, the deposited material crystallizes in a lattice structure and orientation identical to those of the substrate. Ideally, a 2-D film epitaxial structure is formed after several atomic layer depositions onto a substrate. If the material is deposited on a substrate of the same composition, the process is called homoepitaxy. Otherwise, it is called heteroepitaxy.

Without introducing additional forces, the morphology at the initial stage of homoepitaxial growth is, based on the thermodynamic "wetting" model, determined by the minimum of interfacial free energies [Sch00]. Briefly, the smaller one of the total free energy of epilayer/vacuum interface plus the epilayer/substrate interface (fe + fi) and the free energy of the substrate/vacuum interface (fs), decides the "wetting" behavior of the epilayers. The epilayers are supposed to cover onto the substrate homogeneously with a decrease of free energy, when fe + fi< fs. In case of fe + fi > fs, a 3-D island morphology is formed preferentially. The partial uncovering of the substrate decreases the total free energy. Looking to a system with lattice mismatch, we should take into consideration the strain from the lattice mismatch in the growth model. The build-up of strain energy at the interface increases with the initial "wetting" growth of the epilayer, and the increased fi leads to 3-D islands formation. For different systems, a competition between different strain relaxation mechanisms was experimentally found, resulting in either 3-D islands formation without dislocations (coherent islands) or the formation of dislocations [Joh97]. Controllable epitaxial semiconductor nanostructures can be synthesized by applying the growth mode of coherent islands, which provides a potential platform for many applications, such as quantum dots devices. For the Ge or GeSi alloy growth on Si (100) substrate, island formations with dislocations were observed [Eag90, Flo99].

The application of the low-dimensional semiconductor nanomaterials requires that, for convenient device integration and processing, position and orientation control over large scales are necessary. Table 1.1 shows a collection of various methods that have been reported so far to realize 1-D semiconductor nanowires at defined locations, with the corresponding scaling range and the literature references. The most common process for position control is based on electron or ion lithographic processing. Herein, for semiconductor nanowire growth, catalyst lithography is the most popular technique for position control. The substrate is patterned by electron-beam lithography, a processing with exposure of a resist layer, metal evaporation, and a lift-off step. Up to date, large area lithographic technologies are confined to scales larger than 32 nm. The growth direction of nanowire is influenced by a lot of factors and positioning of catalysts at well defined locations will not solve the task of controlling position and direction of nanowires. For these reasons, alternative means of down-scaling to small diameters (≤10 nm) are exploited. The surface template method was derived from the selective area growth on a lateral patterned surface. A quantum wire structure was produced on a GaAs(100) substrate with an etched pattern of parallel V-grooves [Bia98]. The epitaxial nanowires had a crescent shape, and with a core thickness in the 10 nm scale. Using the scanning tunneling microscopy (STM) approach with atomic resolution, ultra-thin Cu<sub>3</sub>N nanowires with a width down to 1 nm were demonstrated grown lateral on a single crystalline Cu(110) reconstructed surface [Max09]. To realize vertically aligned nanowire arrays, reactive ion etching (RIE) and patterned metal-assisted etching methods were used, through a self-organized porous mask, decreasing the mean size of nanowire arrays down to the sub-10 nm scale [Hua08]. However, some top-down techniques produce surfaces of nanowires with a high density of defects, by the high energy ion bombardment at the bulk material. Although the crystallographic orientation could be confined vertically to the substrate, the nanowires were found to be tapering with increase of the length to diameter ratio. The surface programmed assembly method [Rao03] does not impose strong demands on the growth process, only proper selective alignment is crucial for well controlled structures. Nanowires & nanotubes are initially, without position control, grown with a fixed growth direction and size. Afterwards, they are collected by a lift-off process and placed on a pre-patterned substrate. A precise single unit alignment is, however, not easily achieved.

| Catalyst lithography | Masked<br>Neutral-beam<br>etching | Patterned<br>Metal-assisted<br>etching | Surface<br>programmed<br>assembly | Surface<br>template | Porous<br>template<br>-assisted |

|----------------------|-----------------------------------|----------------------------------------|-----------------------------------|---------------------|---------------------------------|

| 50-100 nm            | Sub-10 nm                         | Sub-10 nm                              | Sub-10 nm                         | 1-2 nm              | Sub-10 nm                       |

| [Fan06],             | [Kub07]                           | [Hua08]                                | [Rao03],                          | [Max09]             | [Rya03],                        |

| [Boo10]              |                                   |                                        | [Lee06]                           |                     | [Zsc07]                         |

Table 1.1 Collection of methods to realize 1-D semiconductor nanostructures at defined locations, with the corresponding size scale and literature references.

The criteria periodicity, small diameter, and vertical alignment of the nanowires can be fulfilled by the assistance of self-organized porous templates. Either a liquid or a gaseous precursor can be used for the growth. A supercritical fluid (SCF) inclusion technique combined with a mesoporous silica film was developed, which produced ordered semiconductor nanowire arrays with several nanometers in diameter [Col01, Wan07]. The high-diffusivity of the fluid enables a rapid transport of the precursor into the mesopores of the silica film. However, rigorous safety precautions should be taken into consideration in these experiments, because of the high pressures and temperatures used to allow nucleation and growth [Han03]. The ideal growth of semiconductor nanowires is supposed to be bottom-up epitaxial growth. Selective bottom-up filling in the vertical 1-D direction can be realized by a combination of VLS growth and porous template with catalysts at the tip of nanowires. This means no template sidewall deposition occurs or at least slow rate parasitic growth on the sidewall compared with the nanowire growth rate. Otherwise, cracks or voids affecting conductive properties of products would be inevitable. At this point, not only high-diffusivity of the source gas is required at the growth temperature, but also the templates have to satisfy the following conditions: (1) ordered pores fitting to the desired size of nanowire growth; (2) chemical stability against source gas and by-products during CVD at the growth temperature; (3) selective deposition of catalyst metal at the pore bottom to enable the epitaxy. Satisfying these conditions, the molecules of source gas can smoothly enter into the pore, being cracked only at the surface of the catalyst with direct contact with the substrate surface.

## 1.3 Heteroepitaxial Nanowire Growth and Crystalline Structure

An enormous amount of work has been focused on fabrication of heteroepitaxial nanostructures which could confine carriers to 1-D quantum wires or to 0-D quantum dots, since the first observation of confinement in a quantum well [Din74]. Compositionally modulated semiconductor nanowire heterostructures and doping modulated nanowire p-n junctions have been produced. The change of the density of states and the Coulomb interactions between carriers in low-dimensional semiconductor nanostructures cause their distinct optical and electric properties. For example, single-nanowire photoluminescence, electrical transport and electroluminescence measurements show the unique photonic and electronic properties of these nanowire heterostructures, and suggest potential applications ranging from nano-barcodes to polarized nanoscale LEDs [Gud02]. Axial heterostructure nanowires were first demonstrated in 1994 for the GaAs-InAs system [Yaz94]. Further development of axial InAs/InP superlattices with atomically perfect interfaces was realized, and a conduction band off-set of 0.6 eV was deduced from the electrical current measurement, due to thermal excitation of electrons over an InP barrier [Bj ö02]. For a lateral heterostructure, spatial separation of subband energies leads to a carrier confinement and a reduced carrier scattering, due to confinement of carriers in the radial direction. For example, Lieber's group used band-structure design and controlled epitaxial growth to create a 1-D hole gas system in Ge/Si core/shell nanowire heterostructures, with ballistic transport through individual 1-D subbands and long carrier mean free paths at room temperature [Lau02, Luw05]. Furthermore, most of the interesting physical behaviors are only observed from true quantum heterostructures, in which their lateral size should be on the scale of 10 nm or less, to be comparable to the de Broglie wavelength of charge carriers. Geyer et al. have demonstrated that, by a top-down method, the diameter of Si nanowire arrays containing Si/SiGe superlattices could be scaled down to sub-20 nm [Gey09].

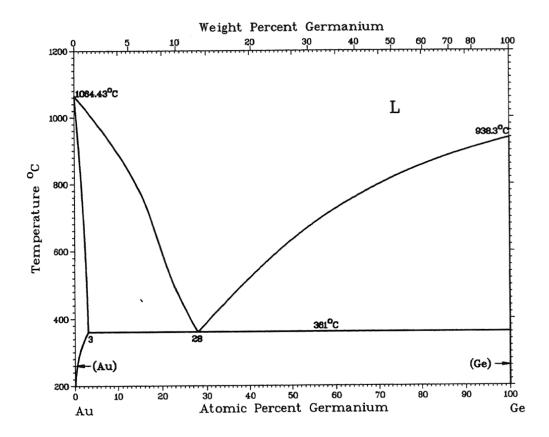

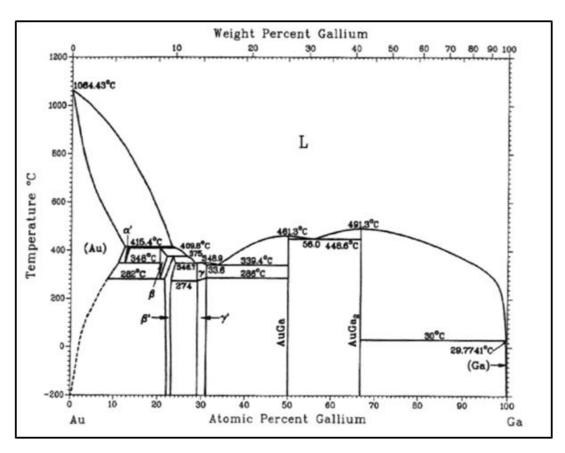

To create an abrupt carrier-confining potential, the interface between the two heteroepitaxial materials must have a high degree of definition. A proper combination of materials has to be considered, because the appropriate growth temperature for each material is generally different. If the traditional VLS mechanism using metal catalyst is responsible for the fabrication of heterostructures in free-standing wires, only a low solubility of the initial target material in the eutectic catalyst allows the growth of compositionally sharp interfaces. For the important two-material system Si-Ge with a similar growth temperature range, however, a sharp interface cannot be achieved by the VLS growth, because of the 19 % and 28% solubilities of Si and Ge, respectively, in the catalytic Au-Si and Au-Ge droplets [Mas90].

For III-V nanowires, experimentally, some combinations show straight nanowire morphology. Persson et al. proposed a vapor-solid-solid mechanism for GaAs nanowire growth [Per04], and Dick et al. demonstrated that InAs nanowires with Au seed particles grow only in the temperature range where the Au-In alloy was believed to be in a solid state [Dic05]. It was noted that the solid solubility of group V elements, such as As and P in Au is less than 1 at.% [Mas90]. Thus, for a heterostructure consisting of the combinations GaAs-GaP and InAs-InP, a high possibility of compositionally sharp heterostructure interfaces in nanowires is expected. However, by changing the growth order for the two materials, most combinations do not provide straight shape in each case. For example, GaP nanowires grown on InP nanowires were straight, but InP nanowires grown on GaP nanowires were kinked [Dic08]. Based on the thermodynamic "wetting" model, a similar behaviour of the crystallization at the initial stage for the epitaxial growth of nanowires can be deduced from the catalyst-free case. Instead of the surface free energy, the interfacial free energies between each of these materials and the catalyst alloy should be considered. Generally, layer growth beneath the catalyst leads to the straight morphology, while islands growth on the initial crystallization position results in the kinked structure. The model described here does not include the consideration of the strain accommodation from lattice mismatch. Without a thin enough mismatched interlayer to release the force by elastically surface deformation, islands tend to form to relieve the built-up strain after growth of a few layers, which finally results in a kinked heterostructure. Other effects, such as changes in catalyst composition affect the interfacial energies, and thus could potentially be used to tune heterostructure morphology by an appropriate choice of growth conditions.

Besides the occurrence of dislocations and kinked structures, we should take into account another special feature existing in III-V heteroepitaxy. The crystalline structure of III-V nanowires is quite different from its bulk counterpart or other low-dimensional heteroepitaxial structures (superlattices, quantum dots). Most III-V NWs have a strong tendency to adopt the hexagonal wurtzite (WZ) crystallographic structure, even though their bulk counterparts are strictly dominated by the cubic zinc blende (ZB) structure. For example, it is possible to grow InAs nanowires with WZ structure, however, WZ is non-existing in the corresponding bulk material where the ZB structure prevails [Kog92]. It is also necessary to find proper growth mechanism working on the heteroepitaxial growth of III-V nanowires in a certain crystalline phase, either in a WZ phase or dominated by the ZB phase. Commonly, the WZ nanowires in many samples contain parts of ZB structure, which show up as stacking faults or as continuous segments. A polytypic structure along the growth axis is even controllable with sharp phase transition [Alg08]. In reality,

nanowires with diameters of tens of nanometers usually appear with a polytypic structure along the growth axis. The phase transition between these two structures obviously affects its physical properties, such as symmetry of the band structure and electron or hole transport along the wire. Woo *et al.* demonstrated the strong impact of twin boundaries on the optical emission of a mixture of ZB and WZ domains in InP nanowires grown on Si(111), which were assumed to be efficient recombination centers [Woo08]. Pemasiri *et al.* published the quantum confinement of holes into the WZ sections and electrons into the ZB sections, which results in extraordinarily long recombination lifetime at energies below 1.5 eV [Pem09]. It will be of great interest to extend the investigation of phase stability with scaling-down of III-V nanowires on Si substrates.

Consequently, the heteroepitaxial growth and crystalline structure of semiconductor nanowires have to be investigated and understood before their electronic and photonic properties can be optimized. Based on experimental observations, several possible growth mechanisms have been discussed in order to better control the crystal phase, for both Ge/Si and III-V/Si heteroepitaxial systems.

### 1.4 Impurities & Defects

Practically, a small quantity of impurities has an obvious effect on the physical and chemical properties of all kinds of semiconductors, as well as on the devices. For example, taken one exotic atom like boron into 10<sup>5</sup> silicon atoms, the conductance of intrinsic Si increases by three orders of magnitude. In crystalline semiconductor materials, much more complicated phenomena are caused by crystallographic defects. The requirements for production of CMOS devices limit the density of dislocations to as low as 10<sup>3</sup> cm<sup>-2</sup> [Mil73]. The introduction of impurities and defects destroys the symmetry of periodic potential in the host lattice, and changes the band structures consequently. Unintentional impurities can affect the carrier concentration. For example, the VLS process uses a metal catalyst, introducing the possibility of metal contamination. The catalyst gold in particular introduces deep levels in silicon and acts as a recombination centre for free carriers.

Impurities in semiconductors can be located on substitutional sites, interstitial sites, or are incorporated as impurity complexes. Examples for such impurities are group-III and group-V elements used in p-type and n-type silicon doping (P, B, As, Al and Ga), and group-IV elements in III-V doping (C, Si). These impurities are shallow, i.e. their ionization energy is comparable to the thermal energy kT. That is, at room temperature, the concentration of free carriers can be considered as similar to the density of impurities, ignoring recombination and compensation effects. Thus, shallow impurities are of great technological importance to determine the conductivities and the carrier types. For high-performance FETs, doping the source and drain contacts as high as possible is crucial to reduce the contact series resistances [Jav05]. Crucial issues for the realization of semiconductor nanowire-based electronic devices are the quantitative and spatial doping control in the wire and the implementation of effective methods to characterize electrically active impurities and their distributions. The in-situ synthesis of doped nanowires during a VLS growth is, depending on the gaseous doping sources, a high-controllable doping method [Zhe04, Sch09a]. In previous works, doped Si nanowires were characterized intensively

with conductance measurements, by placing an isolated Si nanowire between electrodes with the help of e-beam lithography [Cui00, Yuj00], or by contacting single NWs with conductive tips inside a scanning electron microscope (SEM) [Kan08]. In contrast, electron holography [Den09] and Raman spectroscopy are simpler and more reliable methods because no electrical contacts between NWs and electrodes are required. Imamura *et al.* reported that, by analyzing the Fano spectral shapes, the active boron concentrations could be characterized along the growth direction of single p-type SiNWs grown by a VLS process [Ima08]. The Fano resonance is due to the interference between scattering from discrete optical phonons and the photoexcited carriers [Gup03]. Disadvantages of this method are the small sensitivity below a doping level of  $10^{19}$  atoms/cm<sup>3</sup>, and almost no sensitivity to n-type doping because a minimum density of active donors of  $4 \times 10^{19}$  atoms/cm<sup>3</sup> is required to observe the Fano line-shape in n-type silicon [Nic00]. Limited spatial resolution is another hindrance for some applications, therefore, atom probe tomography was used to analyze the quantitative and spatial dopant concentrations in arbitrary position of a single nanowire [Per09]. This method displays atomic resolution, but is insensitive to electrical activity.

The impurities are introduced into III-V compound nanowires in a more complicated way. The growth of III-V nanowires by chemical-beam epitaxy (CBE) employs gas sources for both the group-III as well as the group-V elements. Although an ultra-high vacuum chamber is used to avoid further contamination, the precursors are metallorganics and the incorporated element is usually attached to three alkyl molecules. The alkyl groups most frequently used are derived from methane (CH<sub>4</sub>) and ethane (C<sub>2</sub>H<sub>6</sub>). Veuhoff et al. reported the use of trimethylgallium (TMGa) and arsine for the growth of GaAs [Veu81], in which high p-type conductivity was obtained as a result of the carbon incorporation. Carbon is known as a stable p-type impurity in GaAs which makes the TMGa precursor an attractive choice for highly p-type doped GaAs. Furthermore, the impurity background concentration of Al<sub>x</sub>Ga<sub>1-x</sub>As was found to be very high, typically in the 10<sup>17</sup>-10<sup>19</sup> cm<sup>-3</sup> range [Dee04]. Such high background impurity concentrations in Al<sub>x</sub>Ga<sub>1-x</sub>As are due to the high reactivity of Al which tends to form strong Al-C bonds (which are stronger than the Ga-C bonds). One should also consider that Si doping might occur in the heteroepitaxial growth of III-V nanowires on Si substrate using Au as catalyst. This is related to Au-Si alloy formation between the Au nanoparticle and the Si substrate working as a Si reservoir. Considering that all group-IV impurities are amphoteric, Si may autocompensate strongly at high doping levels. Even though, Si introduces predominantly n-type doping in III-V semiconductors, and is a shallow donor with 4-6 meV ionization energy in GaAs and InP [Sch93].

A specific challenge for obtaining compatibility of semiconductor nanowire growth with CMOS processing is, that the metal catalyst can behave as a deep-level impurity contamination in silicon. Au produces a deep level close to the middle of the silicon band gap with high recombination efficiency. Therefore, one of the most significant issues is the elimination of Au from the process. Since Au is difficult to remove completely after growth [Woo07], catalysts compatible with CMOS requirements or catalyst-free growth techniques must be developed. Several non-gold catalysts were successfully adopted for the growth of Si nanowires [Giv75, Kar00, Gar07]. The epitaxial growth of Al catalyzed Si NWs via VSS growth mechanism is a promising solution [Wan06]. The control of size, growth direction, and crystal quality using Al catalyst has been

demonstrated in Chapter 4. The new discovery of silver as catalyst for gallium phosphide nanowire epitaxy will be discussed in Chapter 6. Deep levels can be caused not only by impurities, but also by point defects or spatially extended defects. Examples for extended defects are dislocations and nanowire surfaces. The surface depletion region can compensate shallow dopants and, as a consequence, reduce the conductivity. Recombination happening on the nanowire surface can drastically degrade the performance of minority carrier devices such as light-emitting diodes, lasers, and bipolar transistors. The optical properties of semiconductor nanowires can be strongly affected by deep traps. Optical measurements of the sub-10 nm diameter GaP nanowires are analyzed with regards to the large surface-to-volume ratio in Chapter 6.

Still, our understanding of 1-D semiconductor nanowire growth mechanisms, as well as the effective characterization of their physical properties is incomplete. The state-of-the-art growth techniques offer limited control of structural and crystallographic properties and at doping. Efforts on improving synthesis techniques have stimulated 1-D nanomaterial research, and a proper understanding of their unique properties is the driving force behind the semiconductor nanowire-based device applications.

## **Chapter 2**

## Anodic Aluminium Oxide (AAO) Combined with Si Growth

In this chapter, first a short introduction on the development of anodic aluminium oxide (AAO) templates is given, and later its application as growth template for semiconductor nanomaterials is described. Our experimental setups for both the AAO template synthesis and the growth of semiconductor nanowires are specified here. Afterwards, two different methods for combination of AAO and Si substrate will be presented respectively, as well as a confirmation of the selective growth of Si inside the AAO templates.

#### 2.1 Introduction

Porous AAO synthesized by electrochemical oxidization of aluminium has been studied and used in numerous fields for more than half a century [Kel53, Boo55]. Based on a two-step anodization process, in 1995, a self-ordered porous AAO membrane with 100 nm interpore distance was first reported by Masuda and Fukuda [Mas95]. The long time first anodization results in an equilibrium morphology at the oxide/metal interface, which shows a textured aluminium surface after removing the first oxide layer. The textured aluminium surface results in highly ordered hexagonal pore arrays in the second anodization step. Since this discovery, AAO can be used to provide ordered honeycomb nanopore arrays, perpendicular to the surface. Most importantly, the diameter of AAO pores can be controlled from a few nanometers to several hundreds of nanometers depending on the anodic voltage and acid species used for anodic oxidation. To date, the most popular model for the self-adjustment of ordering in AAO is based on the mechanical stress, which is associated with the expansion between neighboring pores during the oxidation process [Jes98]. Under conventional so-called 'mild anodization' (MA) conditions, AAO formation is described by a 10% porosity rule, corresponding to a volume expansion ratio of 1.2 between aluminum and alumina [Nie02]. Lee et al. reported that, by using the so-called 'hard-anodization' (HA) process, well ordered hexagonal pore arrays in AAO can be produced with a growth rate 25–35 times larger than with MA but a smaller porosity rule of only 3% [Lee06a].

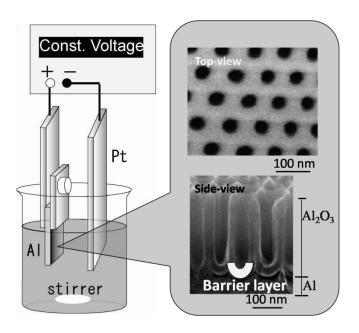

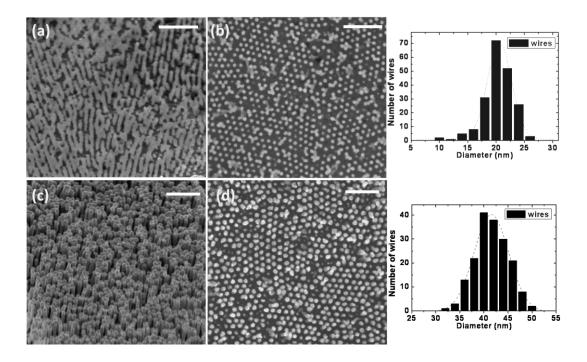

Anodization can be carried out under constant voltage mode (potentiostatic) or constant current mode (galvanostatic). In general, a two-step constant voltage anodization is recommended (Fig 2.1). The experimental setup is quite simple as shown on the illustration of Figure 2.1. In order to get homogeneous reactions, the electrolyte is stirred. The structure of pore arrangement after the second anodization is characterized as a close-packed hexagonal pore array (top-view SEM image), and columnar cells containing elongated cylindrical nanopores are normal to the Al surface. Each nanopore is ended by a thin barrier oxide layer with approximately hemispherical shape (side-view SEM image, white insert). Typically, AAO films with different pore diameters and interpore distances ranging from 20 to 200 nm can be prepared, using three major inorganic

acid electrolytes: H<sub>2</sub>SO<sub>4</sub>, H<sub>2</sub>C<sub>2</sub>O<sub>4</sub>, and H<sub>3</sub>PO<sub>4</sub>. The respective electrochemical parameters and dimensional measurements obtained by *ex situ* SEM characterization are shown in Table 2.1. We can conclude that, without further pore widening after the second anodization, the pore diameter after ordering in sulfuric acid is the smallest down to the 20 nm range. The pore density is increased with decreasing of constant voltage, similar to the reported approximately 2.5 nm/V linear relationship [Nie02]. On the other hand, the pore diameter and shape are influenced by the electrolyte temperature and the anodization time because of the chemical etching on the pore wall. For example, the sulfuric acid anodization at 25 V results in a minimum pore diameter of 20 nm at 1 °C rather than the 25 nm at 8 °C.

Figure 2.1 Simplified illustration of the experimental setup of a two-step constant voltage anodization. The structure of the AAO film was characterized by top-view and side-view SEM images.

Table 2.1 Recommended electrochemical parameters for ordered AAO preparation.

| Electrolyte                    | Concentration | Voltage | Temperature | 1 <sup>st</sup> | Oxide               | Pore          |

|--------------------------------|---------------|---------|-------------|-----------------|---------------------|---------------|

|                                |               | (V)     | (℃)         | anodization     | etching             | diameter(nm)/ |

|                                |               |         |             | time (h)        | $T(^{\circ}C)/t(h)$ | interpore     |

|                                |               |         |             |                 |                     | distance(nm)  |

| H <sub>2</sub> SO <sub>4</sub> | 0.3 M         | 25      | 1 ~ 8       | 20 ~ 40         | 60/16               | 20/65         |

| $H_2C_2O_4$                    | 0.3 M         | 40      | 1 ~ 8       | 20 ~ 40         | 60/20               | 40/100        |

| H <sub>3</sub> PO <sub>4</sub> | 1.0 wt. %     | 195     | 1 ~ 2       | 16 ~ 20         | 45/24               | 180/500       |

AAO has been used as a template for fabrication of various nanomaterials since it has many advantages [Mar94], such as small pore diameter, high packing density and much lower cost compared with conventional lithographic techniques. Its application was a breakthrough in the preparation of ordered 1-D nanomaterials, such as in the fields of metal nanowire arrays [Sau02], carbon nanotube arrays [Iwa99], vertical ultra-high density magnetic storage media [Chu05] and

photonic crystals [Nak99]. In addition, thermal and chemical stabilities of AAO are high enough for VLS growth of Si NWs, since the main component is a stable material. Early experiments using AAO as templates to grow semiconductor nanowires have been done with free standing membrane without epitaxy [Xud00, Car01]. Ordered vertical nanowires would allow a higher packing density than the presently used lateral structures. If nanowires are grown epitaxially on the substrate from defined catalyst locations, for integration convenience, the wires can be left in place, and the contacts can be post-processed to the exposed top of the wires. One approach presented in literatures utilized a thin aluminum film on a conductive substrate [Chu02]: the electrochemical formation of aluminum oxide stops as soon as all Al metal is consumed, and the thinner AAO barrier layer formed on the conductive material can be removed by chemical etching. In this case, the AAO membranes are fitting and connected to the substrate. A big advantage of a fixed AAO membrane on a substrate is that the AAO nanopores can be used as template to control the epitaxial growth direction of semiconductor nanowires perpendicular to the substrate surface, even if the direction is not a preferred orientation of nanowire growth in free space.

#### 2.2 Experimental Setup

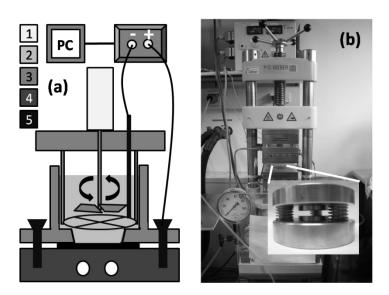

Figure 2.2 (a) Schematic drawing of the apparatus used for the AAO anodization. A computer (PC) controlled the potentiostat (Keithley Sourcemeter 2400). The different greyscales from 1 to 5 represent respectively: 1. Motor-controlled rotator for agitating the electrolyte; 2. Cooled electrolyte sealed in the cell with heat isolation by the thick Teflon walls; 3. Main electrochemical cell and rotating stirrer made of Teflon; 4. Copper plate working as electric conductor and cooling element; 5. Aluminum sheet, metallic screws for fixing the cell to the copper plate and connecting the anode, and Pt mesh working as counter electrode connected to cathode. (b) Photograph of a hot-plate manual lab press (PW 40 TEMPRESS; P/O/WEBER) used for bottom-imprint method. The insert shows a home-made counter-part designed for small samples.

Figure 2.2a shows a schematic drawing of our apparatus for electrochemical anodization. The Teflon made electrochemical cell consists of mainly two separate parts: one is the electrolyte

container which is fixed by screws to the copper cooling plate, and the Al sheet is sealed between the electrolyte and the conductive cooling plate worked as anode; the other part with platinum (Pt) mesh acting as the counter electrode (cathode), and a motor-driven agitator is used to stir the electrolyte. For effective cooling of the Al sheet during anodization, a combination of cooled electrolyte with thick Teflon wall sealing is employed. The sourcemeter for anodization is controlled by a computer, with a working capability of either 0-200 V (potentiostatic mode) or 0-100 mA (galvanostatic mode). Figure 2.2b shows a device used for the bottom-imprint method, which will be discussed in details in Chapter 4. The two pressing plates can be heated with controllable temperature, and the insert shows a home-made counterpart with ultra-flat surfaces of single-crystal sapphire wafers.

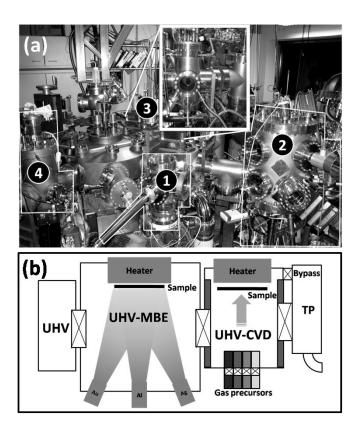

Figure 2.3 (a) Photograph of the main UHV system consisting of: No.1 load-lock chamber, No.2 MBE chamber, No.3 CVD/CBE chamber, No.4 heating chamber. (b) Schematic drawing of the MBE chamber for catalyst deposition, and the CVD chamber for nanowire growth.

Figure 2.3a shows our main UHV system for semiconductor nanowire growth. Several functionalized chambers are connected to the main vacuum chamber which has a background pressure below  $1\times10^{-10}$  mbar. No. 1 as outlined is the load-lock chamber for inserting samples into the UHV chamber. It also works as a pretreatment chamber for pumping away the remaining chemicals, especially absorbed inside the AAO pores, such as the volatile chloroform. One of the functionalized chambers for deposition of catalytic materials is No.2, an UHV-MBE system with multiple crucibles. A radiative heater with temperature control placed inside was designed to observe the growth of catalysts at certain temperatures with an *in situ* reflection high-energy electron diffraction (RHEED) characterization. This chamber is also used for the metal decoration

method to tremendously shrink the size of metal catalyst particles. The most important chamber is No.3 (enlarged as inset in Figure 2.3a), which can be either used in a CVD growth mode (total pressure in the range from  $1\times10^{-2}$  to  $1\times10^{1}$  mbar) or in a CBE growth mode (from  $1\times10^{-5}$  to  $1\times10^{-5}$ 10<sup>-4</sup> mbar). To enhance the efficiency of gas precursors, this chamber was designed with a dual-wall structure with water-cooling and compact volume. The heater with a PID controller (Eurotherm 216e) can be set from room temperature to 750 °C. The temperature was calibrated by a measurement with five thermocouples glued on a standard 100 mm Si wafer. The flow rate of silane gas is controlled by a mass flow controller (MKS 647B), while the other gas precursors were introduced from the lower part of the chamber by manually adjusted gas dosing valves of separate channels. For phosphor doping during Si nanowire growth and gallium/indium phosphide nanowire growth, gaseous tertiarybutylphosphine (TBP) is pre-cracked by a tubular gas cracker settled inside the chamber. No.4 is a water-cooled dual-wall UHV-heating chamber used for the surface reconstruction of Si wafers, with a heating capability of 800 °C at 1×10<sup>-9</sup> mbar. A simplified schematic cross-section drawing of the two main process chambers respectively for catalyst and nanowire growth is shown in Figure 2.3b. The sample (Si wafers in most cases) is first transferred from the main UHV chamber into the MBE chamber for catalyst growth. High purity (≥99.999%) reservoirs of Au, Al, and Ag inside thermal evaporation crucibles are mounted with a fixed angle relative to the sample position. Afterwards, the sample with deposited catalyst can be in situ transferred into the CVD chamber for nanowire growth.

#### 2.3 AAO Growth on Si

In order to use AAO as a scaffold that separates and aligns semiconductor nanowires or nanotubes for integration with Si-based CMOS technologies, AAO membranes connected directly to the Si substrates are desirable. As formed on bulk Al sheet, AAO films can be provided with highly ordered honeycomb nanopore arrays. They are produced by an electrochemical polishing of Al and a two-step anodization [Mas95]. If the thin Al film is deposited on the Si substrate and anodized, the ordering of AAO is difficult to be achieved due to the complicated surface roughness and nonuniform crystallite sizes [Hil08]. The surface condition of the Al film will directly affect the ordering of the grown nanopore arrays. However, with pore formation guided by lithographical or imprinted surface patterns, controlled pore ordering and independently controlled pore spacing can be realized [Rob07].

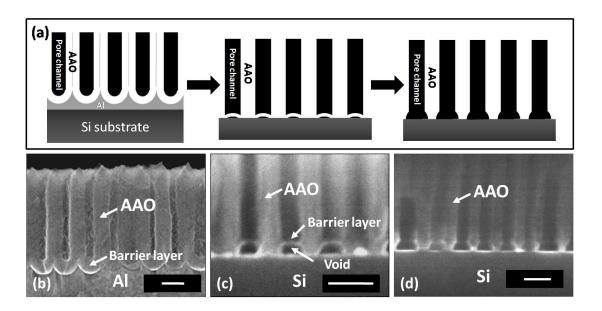

Figure 2.4a is a schematic illustration of Al anodization on Si substrate, the barrier layer formation, and the morphology of the AAO/Si interface after removal of the barriers. First, a thin Al layer (thickness  $< 1 \mu m$ ) was sputtered onto the H-terminated n-type Si(100) substrate. A standard anodization for the fabrication of AAO with 40 nm pore diameter was performed. The pore formation process proceeds with a thick barrier layer underneath as shown in Figure 2.4b. The normal anodization stops as soon as the Al below the center of the pore is oxidized. The anodization can be continued until it consumes all of the aluminum beneath the barriers. When this process is continued, the resulting oxide barrier layer structure at the bottom of the pores is, as shown in Figure 2.4c, quite different from the morphology in the bulk aluminum. A void structure is observed beneath a thin arch-shape barrier layer bended upwards at the end of each pore. Forces

on already existing oxide by newly formed oxide combined with geometrical conditions produce the upward bending [Cro00].

Figure 2.4 (a) Schematic illustration of AAO anodization on Si substrate, barrier layer formation, and the pore opening by etching off the barriers. (b) - (d) Side-view SEM images corresponding to each single process illustrated in (a), respectively. Scale bars are 100 nm.

To confirm the growth mechanism responsible for the arch-shape barrier layer formed on Si, further analysis of the current-time curve together with the microscopy of the interface is shown in Figure 2.5. The barrier layer touching the Si substrate is shown in Figure 2.5b, corresponding to the current point at A in the I-t curve in Figure 2.5a. Further anodization creates additional dissolution of the barrier near the Si, and the increase of current from point A to point B is explained by a resistance decrease. Schematic inserts illustrate the stresses at the interfacial region and the growth of silicon dioxide on Si surface, corresponding to point B and point C, respectively. In contrast to the anodization on the Al sheet, the residual Al on Si in between the neighboring pore-cell as confirmed in Figure 2.5b is firmly attached to the rigid Si substrate. Therefore, the stresses by volume expansion of alumina and silicon dioxide (the directions of stresses are shown by arrows) are accommodated with interfacial restructuring to create the void. During the oxidation of the residual Al, the inverted shape of the barrier layer becomes thinner with further bending. The electrolyte leaks into the voids, through cracks of the barrier caused by bending, and the aluminium oxide is dissolved inside the void as well as at the outside surface. The further anodization of Si instead of Al results in the decrease of current from point B to point C with prolonged SiO<sub>2</sub> growth. The thickness and shape of SiO<sub>2</sub> beneath the pores was investigated with HF selective etching (Figure 2.5d). We found that the Si surface had concave dimples at the position of pore bottoms after removal of the SiO<sub>2</sub> layer.

In conclusion, anodization of an Al film on a conducting Si substrate has two main peculiarities. First, the insulating arch-shape barrier alumina layer with void beneath, which is easy to remove without obvious widening of the pore diameter. Second, the Si surface reacts electrochemically in

a controllable manner, and its oxide thickness can be selected by monitoring the anodization I-t curve after the anodization of Al is complete. In this process, proper switch-off time is crucial in order to avoid the detachment of the AAO from the Si substrate after removing the SiO<sub>2</sub> layer. Inhomogeneities of Al metal film thickness and of current density during anodization result in different optimum anodization times required at different positions of the sample.

Figure 2.5 (a) The evolution of current during the last period of anodization of an Al film on a Si substrate using  $H_2C_2O_4$  solution. The inserts depict the process flow of voids formation with curvature inversion of the thin barrier layer, corresponding respectively to the highest current point (B) and the lowest point (C) in I-t curve when the process is stopped. (b) Side-view SEM image of the AAO/Si interface when the Al beneath the barrier is completely consumed, corresponding to the current point (A) in (a), where remaining Al between neighboring AAO pore cells is visible with bright contrast and triangular shapes. (c) The SiO<sub>2</sub> formation can be confirmed from the concaves beneath each pore after the HF dipping. Scale bars are 100 nm.

## 2.4 AAO Bonding onto Si

As mentioned previously, the approach of anodizing an Al layer on the Si substrate has two main drawbacks. First a good ordering of AAO pores requires a long time etching and a thick and smooth Al film which could not be obtained with available equipment. Second the undesired anodization of Si leads to a rough Si surface with dimples beneath each pore bottom. A new

method was invented based on the idea of processing a freestanding AAO membrane and bonding the thin membrane onto a Si wafer. Instead of filling the pores with an etching solution and simultaneously etching pore walls and the barrier at the pore bottom, a freestanding AAO membrane can be floated on an etching solution, and only the barrier layer contacts to the chemicals.

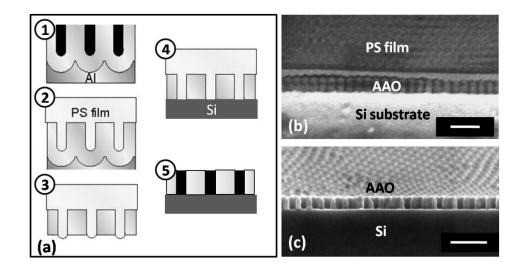

Figure 2.6 Thin AAO membrane bonded onto Si substrate. (a) Scheme for the fabrication: 1) thin AAO film on Al with high ordering, 2) spin-coating of PS film, 3) selective etching of Al substrate and barrier layer, 4) transfer of AAO membrane onto Si substrate, 5) removal of PS. (b) Tilted side-view SEM image of AAO/PS bonded on Si in step 4, scale bar is 100 nm. (c) Tilted side-view SEM image of sample (b) after step 5, scale bar is 150 nm.

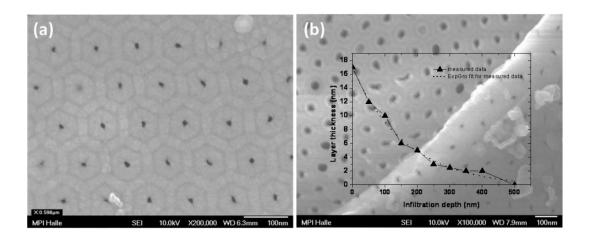

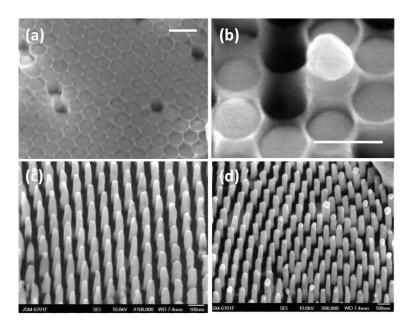

In order to realize a freestanding continuously open AAO membrane bonded onto Si substrate, a polymer-assisted method was used as illustrated in Figure 2.6a. First, a thin AAO film was synthesized by the standard two-step anodization process as step 1. Here we show one sample as an example, because different electrochemical parameters correspond to different pore diameters and interpore distances. Applying a constant voltage of 25 V in 0.3 M H<sub>2</sub>SO<sub>4</sub> acid (3 °C), the first anodization lasted for 24 h. Then, the oxide layer was completely removed by wet etching (a mixture of 1.8 wt. % chromic acid and 6 wt. % phosphoric acid) at 45 °C to obtain a textured surface on Al. The second anodization was conducted with the same parameters as the first one, and only lasted for 180 s for an oxide thickness of about 100 nm. A spin-coating process (step 2) was used to fill into the pores a thin layer of polystyrene (PS), which attached homogeneously to AAO after spinning with 3000 rpm for 60 s using 1.5 wt. % PS/CHCl<sub>3</sub> solution, followed by a 90 °C solidification heating. The protection layer of PS enhances the buoyancy of AAO, and its hydrophobic nature enables the remaining Al substrate to be etched completely by floating on a mixture of CuCl<sub>2</sub> and HCl solutions. It should be pointed out that the thin PS film prevents the thin ceramic membrane from mechanical deformation. The integral structure can be retained during handling and transfer. After removal of Al, the barrier layer was selectively etched by changing the etching solution to 5 % H<sub>3</sub>PO<sub>4</sub> at 30 °C for 15 min (step 3). Since the whole pores were filled by PS, the side-effect of pore widening was avoided. The whole PS/AAO membrane still floating on the surface of deionized water was transferred to a desired substrate such as Si (step 4). One sample is shown in Figure 2.6b, a tilted side-view SEM image. The AAO has a thickness of around 100 nm with a homogeneous 30 nm thick PS film covering the surface. The pores are sealed and attached to the Si surface. The exterior PS film can be removed by a CHCl<sub>3</sub> washing, and the PS inside the pores can be further dissolved with an immersion into CHCl<sub>3</sub> or vacuum pyrolysis. This process (step 5) not only gets rid of the PS but also enables the conformal contact of the AAO bottom side with the flat Si surface (shown in Figure 2.6c). The pores are oriented along the normal of the substrate.

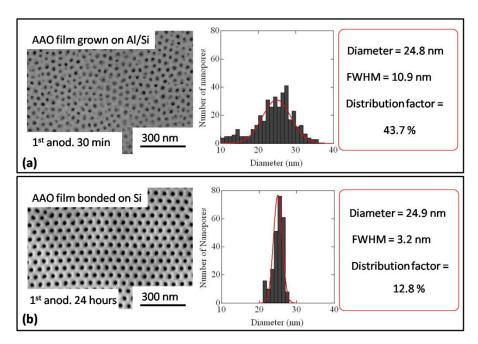

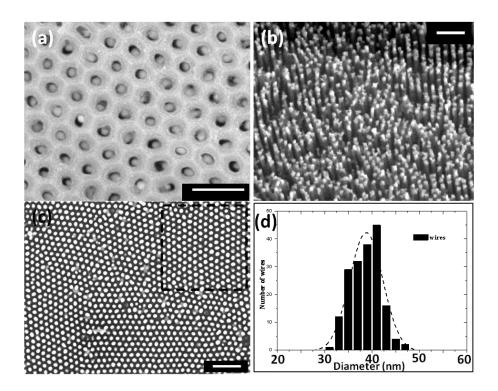

The van der Waals forces at the interface exhibit an excellent contact which can even survive evacuation. The thickness of an AAO film produced with sulfuric acid anodization should not exceed 250 nm, which corresponds to a pore length/diameter ratio of 10. The same ratio limitation was found in the case of oxalic acid, with a 40 nm pore diameter. Beyond this ratio, the PS always filled the pores only incompletely, and conformal contact was impossible because of surface roughness after selective etching. The analysis of pore morphologies of the two AAO/Si integration methods, as shown in Figure 2.7, shows the advantages of the new method. Using the direct growth of Al on Si substrate method (Figure 2.7a) with a short 1<sup>st</sup> anodization, the self-ordering is quite limited, and the pore diameters have a distribution factor (i.e. the ratio of FWHM/mean diameter) above 40 %. Partial pores are branched, and are not perpendicular to the substrate. The new method of thin AAO film bonded onto Si inherits the highly self-ordered pore arrangement caused by a long 1<sup>st</sup> anodization (Figure 2.7b). While keeping the mean diameter with the same potentiostatic voltage, the pore diameter has a narrow size distribution of about 10 %. Judged from the top-view SEM image, the pores are all perpendicular to the substrate and they form close-packed hexagonal array.

Figure 2.7 Comparison of two methods for AAO/Si integration: (a) Anodization of Al film deposited directly on Si substrate and (b) thin film of AAO bonded on Si substrate. Left top-view SEM images of pore morphologies with 1<sup>st</sup> anodization of 30 min and 24 h, right size distribution diagrams together with key parameters.

## 2.5 AAO-Metal-Assisted Chemical Etching

This subchapter describes a complementary method for the production of vertically-aligned semiconductor nanowire arrays. Among various fabrication methods, AAO-metal-assisted chemical etching has gained importance as a low-cost and versatile top-down method for fabricating Si and Si/Ge nanowire arrays [Hua08, Gey09]. In AAO-metal-assisted chemical etching, noble metals such as Au, Ag, and Pt with porous film morphology are used to catalyze etching of Si substrates, in a HF solution containing an oxidant. The noble metal could offer a path for hole injection from the oxidant to the Si substrate. The noble metal catalyzes reduction of the oxidant (such as H<sub>2</sub>O<sub>2</sub>), and therefore accelerates the chemical etching reaction [Tsu07, Lee08]. The Si substrate has a selective fast etching rate just below the noble metal coverage. Consequently, the morphology of the noble metal controls the morphology of etched Si nanostructures.

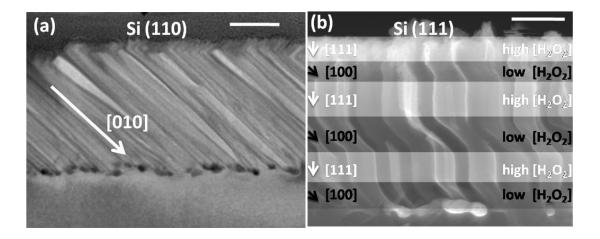

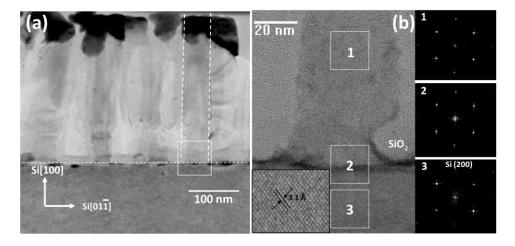

Figure 2.8 (a) Cross-sectional TEM image of Ag particles assisted etching of Si(110) substrate with [010] etching direction, the viewing is along the [001] direction, and (b) cross-sectional SEM image of orientation-modulated etching of Si(111) substrate by periodic control of oxidant concentration [Hua10]. Scale bars are 200 nm.

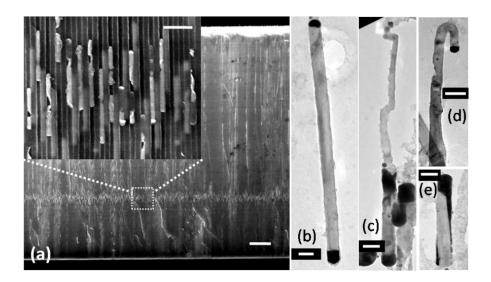

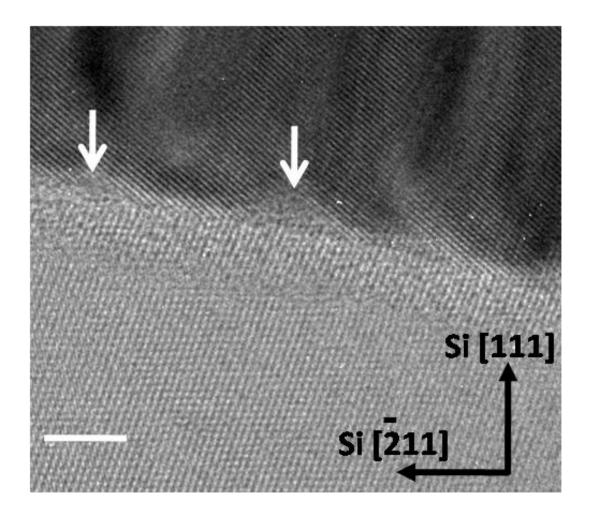

It was demonstrated that metal-assisted chemical etching is also influenced by crystallographic factors and the concentration of the oxidant. Etching prefers to proceed in the <100> directions, even if Si(110), and Si(111) substrates are used. Figure 2.8a is a cross-sectional transmission electron microscopy (TEM) image of Ag nanoparticles assisted etching of Si(110) substrate. The viewing direction is along Si[001]. We observed that all the Ag particles have a similar etching rate along the [010] direction. On the other hand, the etching behavior on Si(111) substrate remained confusing, since in the literature the preferred etching directions were reported as either <100> or <111> directions [Che08]. Illustrated in Figure 2.8b, a side-view SEM image, we found that the concentration of the oxidant allowed a highly controllable modulation of the etching direction of the Si(111) substrate between the [100] direction and [111] direction. In an etching solution with high concentration of oxidant ( $H_2O_2$  0.5 M, HF 4.6 M), the etching occurred in the vertical [111] direction. Whereas in the solution with much lower oxidant concentration ( $H_2O_2$

0.01 M, HF 4.6 M), the etching preferred the [100] direction. Based on this controllable etching, we can realize porous Si nanostructures with periodically modulated pore orientations.

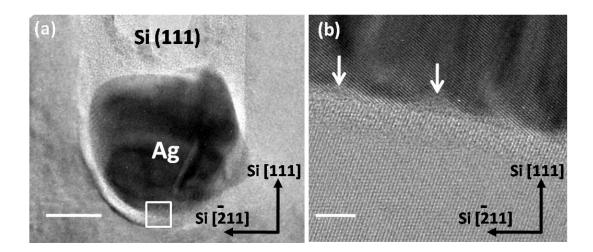

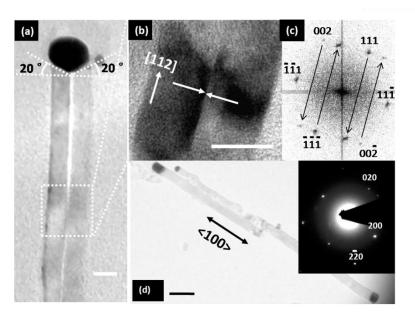

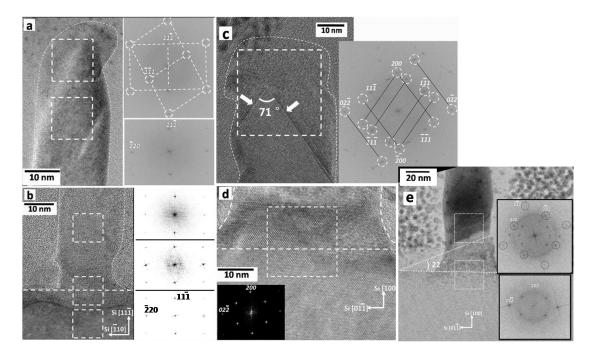

Figure 2.9 (a) Low-magnification of HRTEM image of an Ag particle etching front along Si[111] direction, the enlarged view (b) from the selected region gives the lattice patterns along the interface, with defect positions indicated by arrows. Scale bars in (a) is 20 nm, and in (b) is 3 nm.

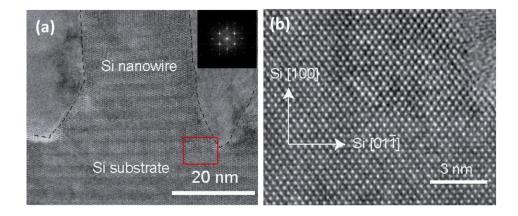

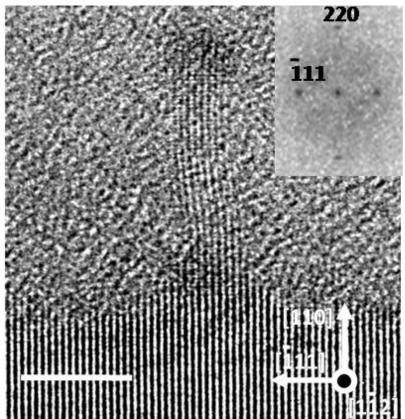

In order to get insight into the crystallographic structure of the etching front (as illustrated in the low-magnification TEM image of Figure 2.9a), a high resolution transmission electron microscopy (HRTEM) image of the interface between Ag particle and Si(111) substrate is presented (Figure 2.9b). The Ag particle has an unsymmetric shape sitting on the top of a pore proceeding along the [111] direction. The etching front is a non-flat interface with a concave shape, where the bright contrast between Si and Ag might be due to the thinner Si or to amorphous oxide formed in between. HRTEM image gives details of crystalline lattice patterns from the selected region on the lowest position. The crossed lattice plans are Si{111} planes with a zone axis of [011] direction. The lattice of Si is tightly connected with the dark-contrast area corresponding to the lattice of the Ag crystal. From the lattice planes, we confirmed that the etching front was not porous but solid without a homogeneous oxide interlayer. We also found that along the interface, at random positions, there are amorphous voids between the two sets of lattice planes (as indicated by arrows in Figure 2.9b). We assume that this is a proof of oxidization of Si at the interface. However, it might be a result of damage caused by the ion-beam thinning process as well.

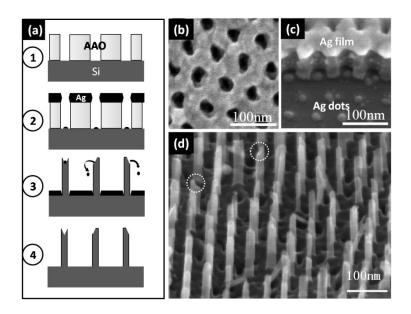

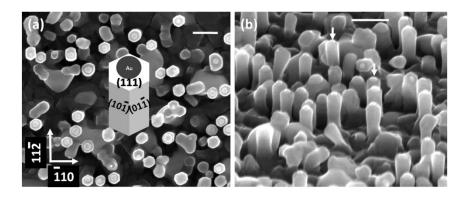

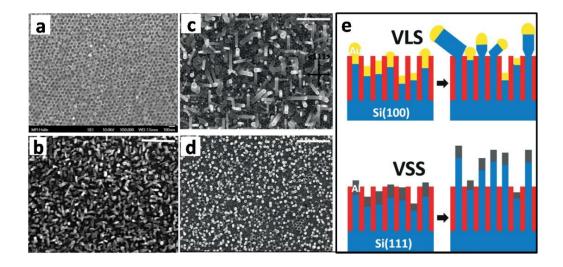

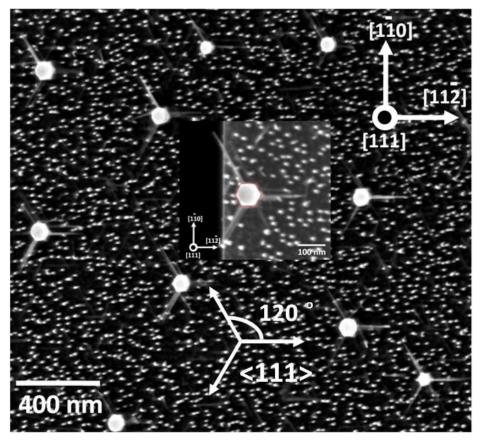

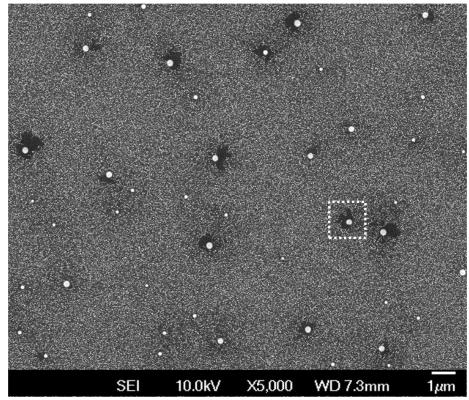

Experimentally, the Ag-particle catalyzed etching was carried out with Si(100), (110), and (111) substrates, and all SEM images showed that the <110> directions are not the crystallographically preferential etching directions. With the assistance of a thin AAO membrane bonded onto the Si substrate, the fabrication of highly ordered vertically aligned [110] Si nanowire arrays was realized by AAO-metal-assisted chemical etching [Hua09]. The schematic fabrication flow is shown in Figure 2.10a: (1) A thin AAO membrane was bonded tightly onto Si(110) substrate by the same procedures as illustrated in Figure 2.6a; (2) Subsequently, a thin (thickness around 20 nm) layer of Ag film was sputtered onto the surface of AAO/Si. With the AAO membrane as a patterned scaffold, the Ag formed a nanoporous film structure with the same pattern (as shown in

the top-view SEM image of Figure 2.10b). Meanwhile, Ag nanodots were also deposited onto the Si surface through the AAO pores (as shown in the tilted-view SEM image of Figure 2.10c); (3) Ag/AAO/Si was dipped into an etching solution, which was a water-based admixture of HF and H<sub>2</sub>O<sub>2</sub>. The AAO sandwiched between Ag and Si was dissolved rapidly by the HF etching through the porous Ag film. The integral Ag film fell onto the Si surface in the solution and started to assist the Si-etching process. During the Si-etching, the lateral vector of the crystallographically preferred <100> etching was suppressed by the interconnected 2-D Ag film. Therefore, the overall etching direction was restricted along [110]. The integral Ag film movement downwards into the Si(110) substrate resulted in the formation of vertically-aligned Si[110] nanowire arrays corresponding to the AAO pattern. Moreover, the isolated Ag particles at each pore bottom could etch into the Si slanting in <100> directions and drop out of the etching of the Si nanowire, leaving the top region of Si initially below the silver partially etched; (4) After the etching ceased, Ag was removed by a HNO<sub>3</sub>-dipping. A Si[110] nanowire array was left, and the partially etched top of wires possessed inclined planes (indicated with the dashed circles in Figure 2.10d). Such details of the nanostructure also confirm that isolated Ag particles move freely in the crystallographically preferred <100> directions. The transition from step 2 to step 3 as illustrated in Figure 2.10a, can only work if the AAO is etched very homogeneously, otherwise it would result in bending and detaching of the Ag layer.

Figure 2.10 (a) Schematic fabrication flow of vertically aligned Si[110] nanowire array by Ag/AAO patterned film etching. (b) Top-view SEM image of the Ag porous film sputtered onto AAO/Si substrate, and (c) its tilted-view SEM image on which the AAO membrane was partly removed, in order to uncover the Ag dots on the Si surface. (d) Tilted-view SEM image of the etched Si[110] nanowire array after silver removal.

#### 2.6 Conclusions

In this chapter, the electrochemical synthesis of ultrathin AAO membranes directly and indirectly

bonded on the Si substrates is studied, respectively. As a crucial part of the production of AAO directly grown on Si substrate, the growth mechanism responsible for the arch-shape barrier layer at the interface was modeled by analysis of the I-t curve combined with microscopy. The etching process of the barrier layer is inevitably accompanied by a pore widening and anodization of Si. This is a disadvantage for practical applications of AAO used as a template for nanowire growth. Therefore, in order to integrate AAO with Si, a polymer-assisted method of bonding a free-standing AAO membrane onto the Si substrate was used. The thin AAO film bonded on Si inherits a highly self-ordered pore arrangement due to a long time 1<sup>st</sup> anodization. Combining the AAO/Si bonding with the metal-assisted chemical etching method, it was revealed that except for the influence of the concentration of oxidant, the crystallographic orientation of Si-etching can be well controlled by the design of interconnected Ag nanostructures.

# **Chapter 3**

## **Epitaxial Growth of Semiconductor Nanowires**

Integration of semiconductor nanowires on the Si platform is essential for device purposes. Therefore, it is highly required to control the crystallographic direction, positioning, diameter, and doping of large area nanowire arrays grown on Si. Innovative template-assisted bottom-up approaches to fabrication and integration of semiconductor nanowires compatible with conventional semiconductor processing will be the subjects of the following chapters. Through a detailed investigation of crystallographic relations in the well-defined nanostructures, we try to understand the different growth mechanisms and the related physics behind.

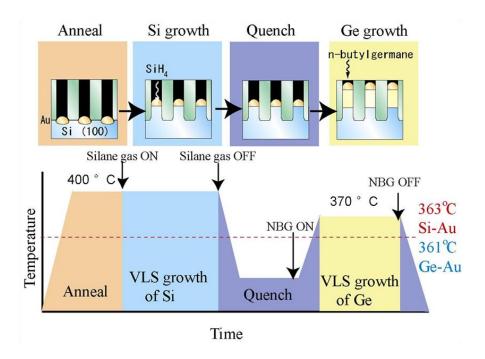

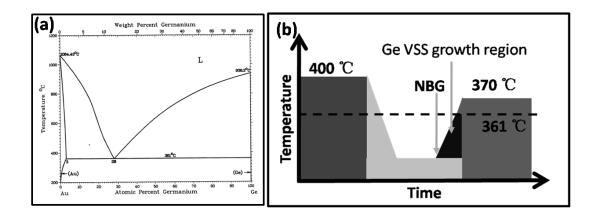

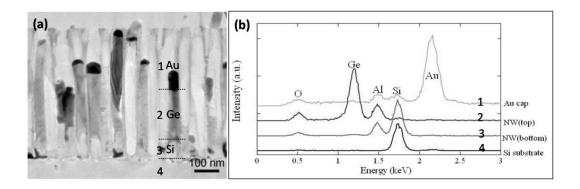

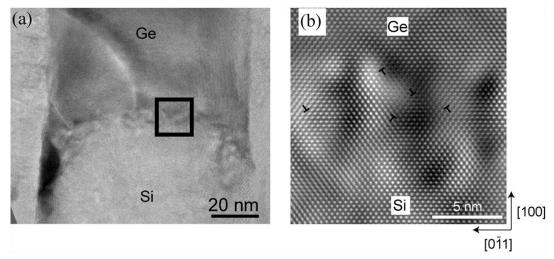

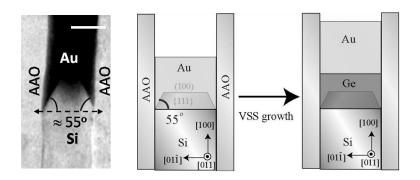

The previous chapter deals with the fabrication of ordered porous AAO nanostructures, as well as their integration with the Si substrates. This chapter will focus on the crystallographic direction control of Si and Ge epitaxial growth with the assistance of AAO templates. The growth mechanism responsible for Ge/Si wire-on-wire heteroepitaxy will be demonstrated. First, the understanding of VLS epitaxy was extended to isotopically enriched Si nanowire growth without template. Later, the growth direction control with AAO templates will be discussed related to the VLS growth mechanism. Finally, a growth mechanism for realizing a sharp interface between two different materials, Ge and Si, with a 4 % lattice misfit is presented, and the experimental results of the Ge/Si heteroepitaxy with a wire-on-wire nanostructure are shown.

#### 3.1 Silicon Nanowire Epitaxy in Free Space

To realize the integration of Si-based 1-D nanoelectronics, the most promising approach is the epitaxial growth of Si nanowires directly on Si substrate with desired crystallographic orientation and doping. Technically, the most widely used method for the high-quality epitaxy is based on a VLS growth mechanism [Wag64, Wag65]. Especially, with the CVD growth technique, the essential concept is a metal/silicon alloy in the liquid-phase working as a medium to transform Si atoms from components of gaseous molecules into a solid crystal. The Si epitaxy is a continuous extension of Si lattice planes from the surface plane of a hydrogen-terminated single-crystal Si substrate.

#### 3.1.1 Introduction

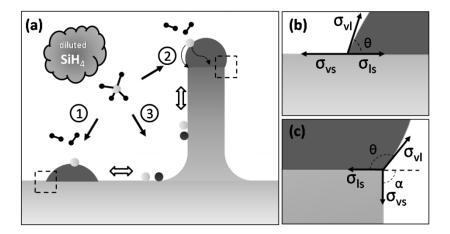

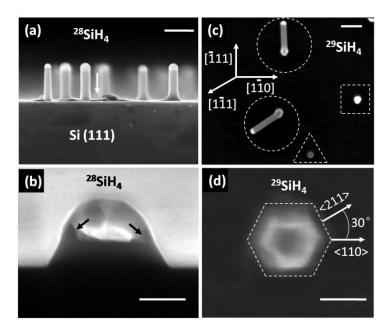

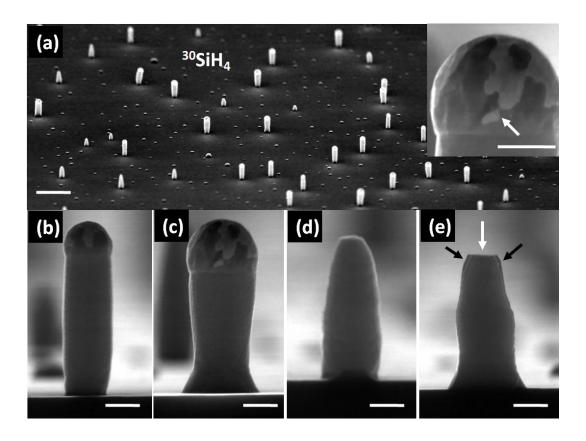

A typical VLS growth model using gold as catalyst is shown in Figure 3.1a. Gaseous molecules with Si components (such as diluted SiH<sub>4</sub>, Si<sub>2</sub>H<sub>6</sub>, and SiCl<sub>4</sub>) are introduced into a vacuum chamber, where an H-terminated Si substrate covered by a deposited thin Au film is heated above

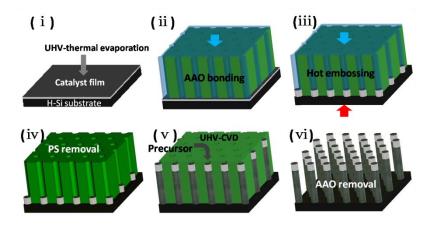

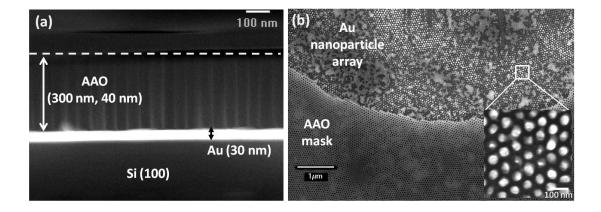

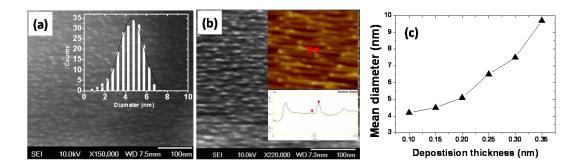

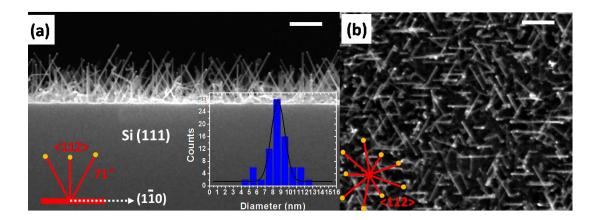

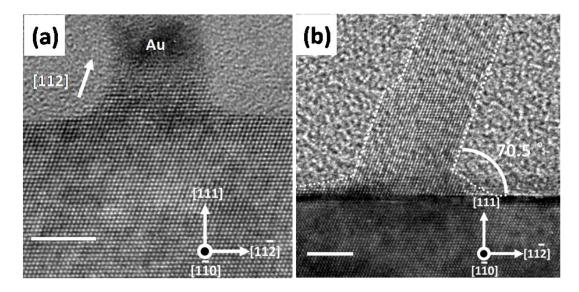

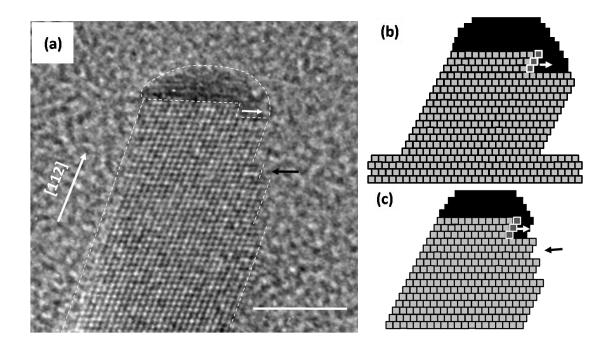

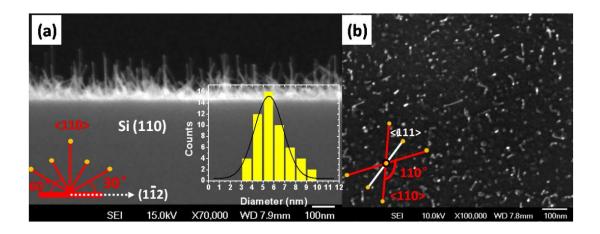

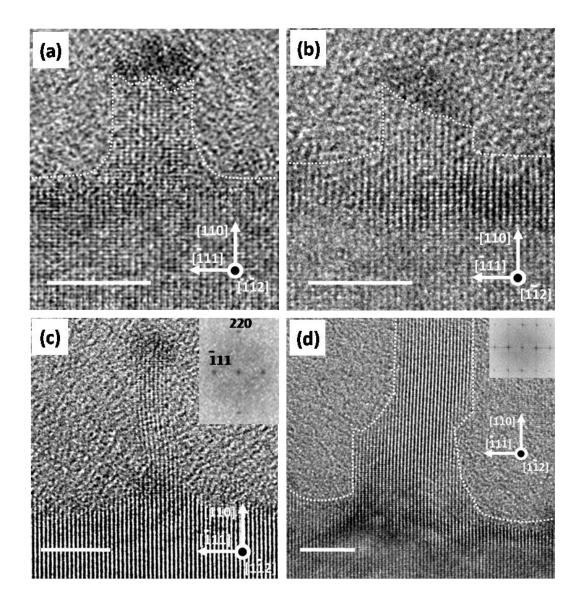

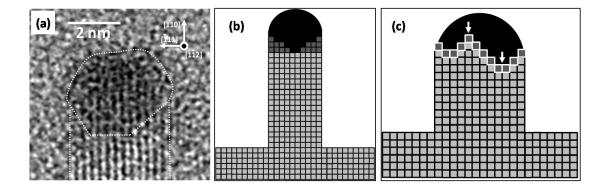

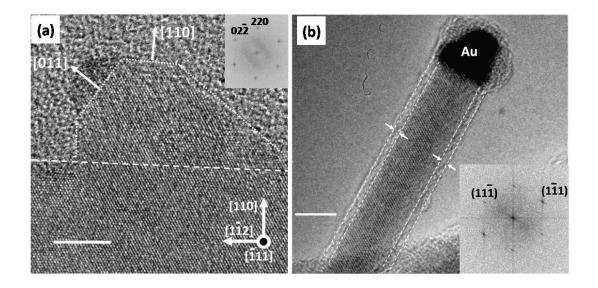

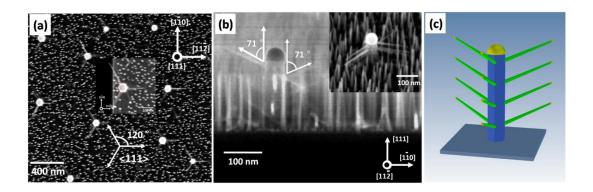

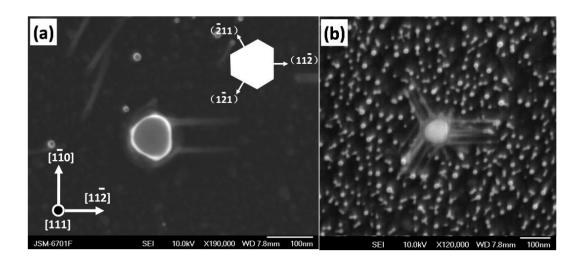

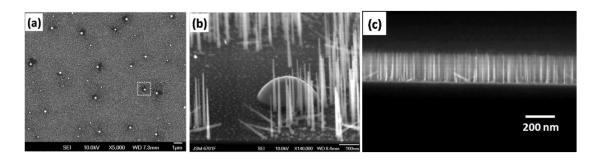

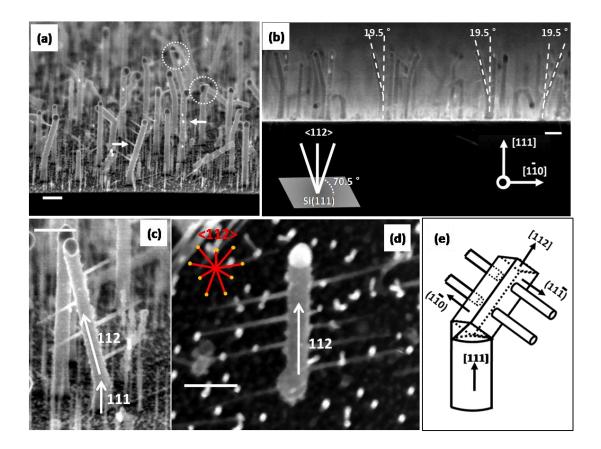

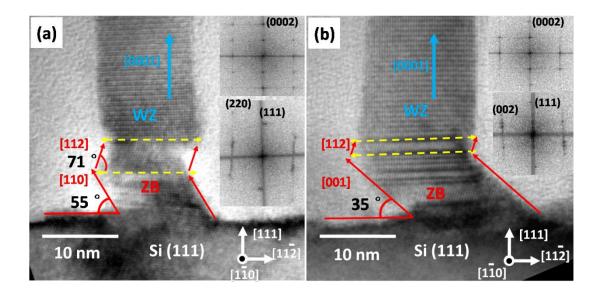

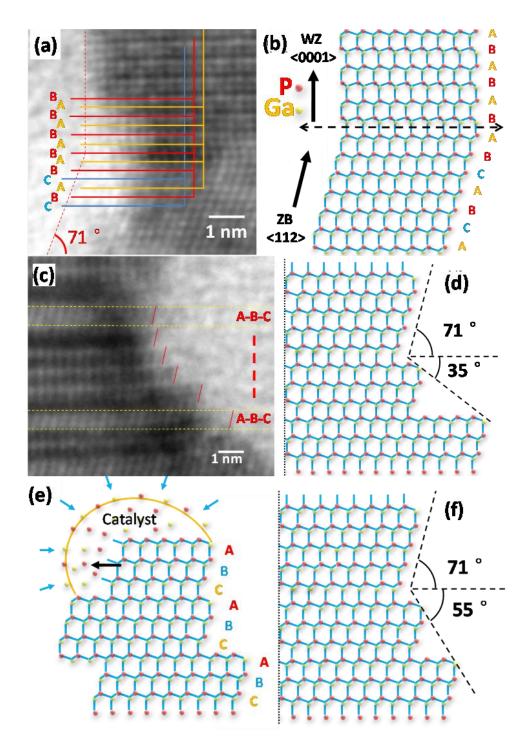

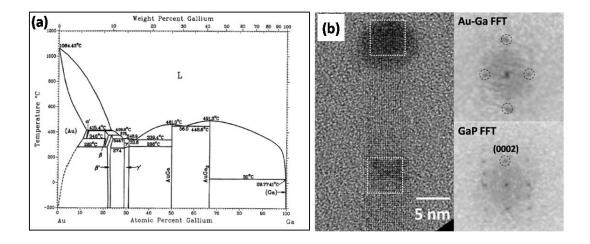

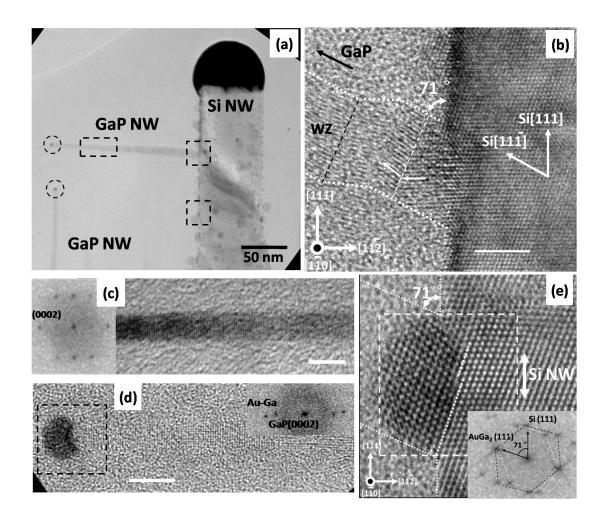

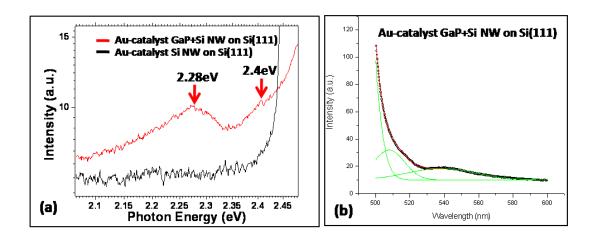

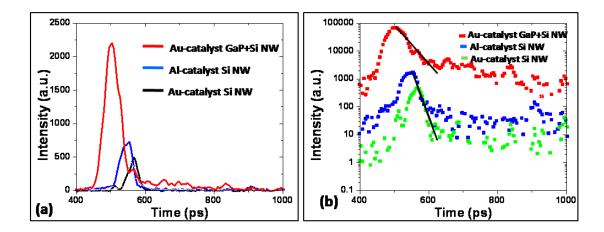

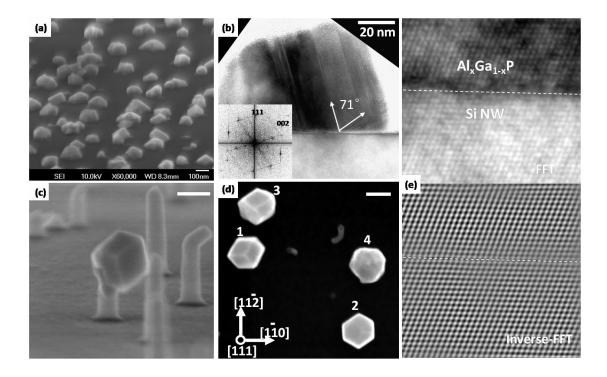

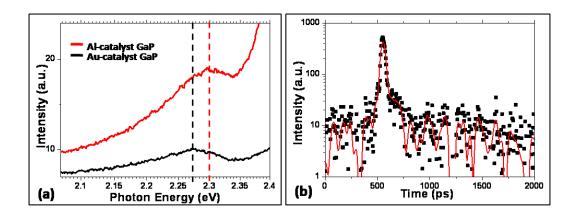

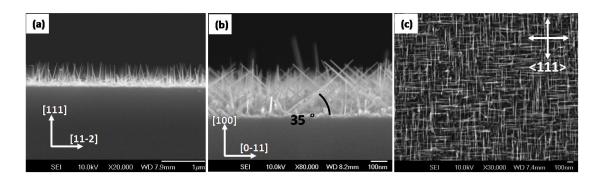

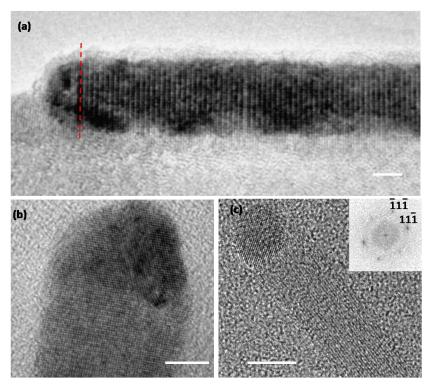

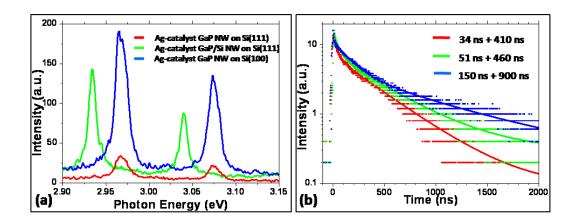

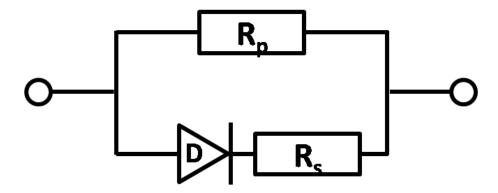

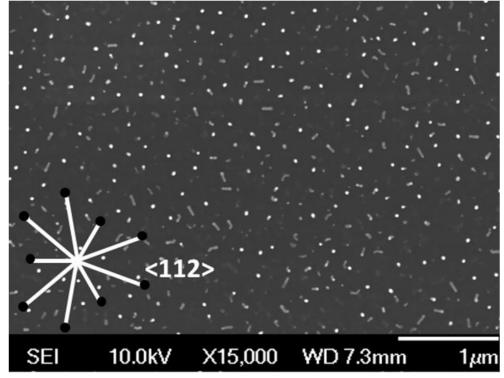

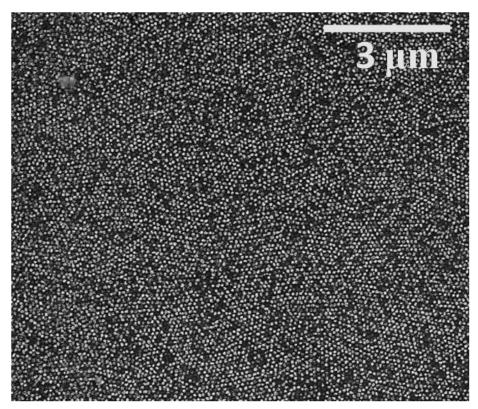

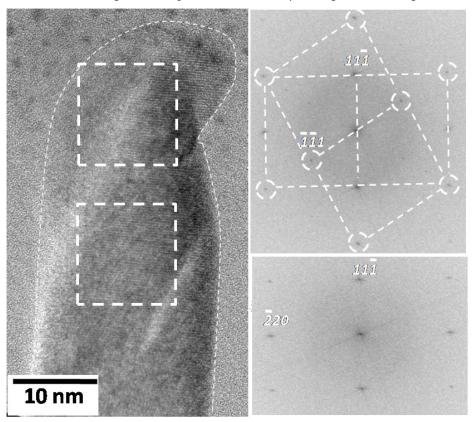

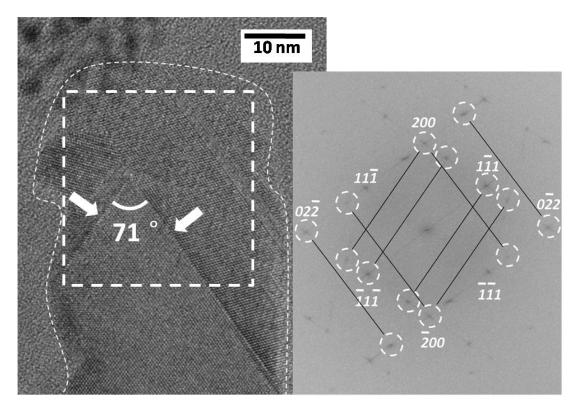

Figure 3.1 (a) Schematic of VLS growth mechanism with Au-Si droplet formation and Si nanowire epitaxy: (1) SiH<sub>4</sub> decomposed on Au-Si eutectic droplet; (2) Si atoms precipitate at the liquid-solid interface or at the edge at the three-phase line through bulk or surface diffusion, respectively; (3) Si atoms deposited from SiH<sub>4</sub> directly onto the Si surface. Expanded views of selected three-phase line junction areas in (b) initial droplet, (c) nanowire growth.