## Silicon Nanowires: Synthesis, Fundamental Issues, and a First Device

### Dissertation

zur Erlangung des akademischen Grades

doctor rerum naturalium (Dr. rer. nat.)

vorgelegt der

Mathematisch-Naturwissenschaftlich-Technischen Fakultät (mathematisch-naturwissenschaftlicher Bereich) der Martin-Luther-Universität Halle-Wittenberg

von Volker Schmidt geboren am 28. Juni 1977 in Braunschweig

Gutachter /in

- 1. Prof. Dr. U. Gösele

- 2. Prof. Dr. W. Seifert

Halle (Saale), den 28.5.2006

verteidigt am 13.12.2006

#### urn:nbn:de:gbv:3-000011060

[http://nbn-resolving.de/urn/resolver.pl?urn=nbn%3Ade%3Agbv%3A3-000011060]

## Preface

The purpose of this thesis is to illuminate several aspects regarding the synthesis of silicon nanowires, their electrical properties, and the fabrication of a first device made thereof. Following an introductory survey of important results in silicon nanowire research, Chapter 1 deals with silicon nanowire growth from an experimental point of view. After a detailed description of the experimental setup, the wafer preparation, and the growth procedure, experimental results concerning the epitaxial growth of silicon nanowires with gold are presented. Gold is presently the standard catalyst material for silicon nanowire growth. Yet, serious concerns exist, whether silicon nanowires grown with gold as catalyst can ever become compatible with existing electronics fabrication technology. Therefore, replacing gold by an alternative catalyst material is of great importance. In the second half of Chapter 1 we present silicon nanowire growth results using different catalyst materials: palladium, iron, dysprosium, bismuth, indium, and aluminum.

The three chapters following thereupon each addresses a fundamental silicon nanowire growth issue. Chapter 2 is devoted to the diameter dependence of the silicon nanowire growth velocity. Since the silicon nanowire length is usually controlled by adjusting the growth time, a knowledge of the factors that determine the growth velocity is crucial. Concerning the diameter dependence of the growth velocity, seemingly contradictory observations were made by different groups. Considering the steady state supersaturation of the catalyst droplet we will derive a model that conclusively explains the differences in the observed behavior. Furthermore, our model links the pressure dependence of the growth velocity to the diameter dependence of the growth velocity; an insight that might be useful for an optimization of the growth conditions. Focus of Chapter 3 is on the diameter increase at the nanowire base that can be observed for nanowires grown via the vaporliquid-solid mechanism on a solid substrate. An explanation for this phenomenon is given in terms of a model that takes the shape of the catalyst droplet into account. In addition, the influence of the line tension on the nanowire morphology is discussed. Chapter 4 deals with the crystallographic growth direction of silicon nanowires, a parameter that is of great importance especially in view of the technical applicability of epitaxially grown silicon nanowires. Experimental results presented in this chapter indicate a diameter-dependent change of the growth direction. We will propose a possible explanation for this growth direction change by taking the interplay of the surface and interface tensions of silicon nanowires into account.

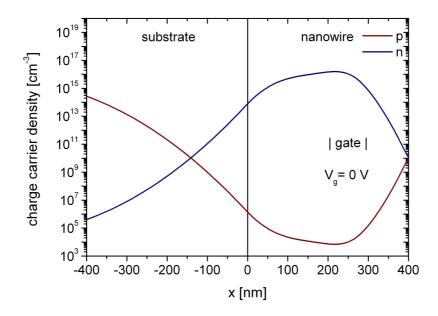

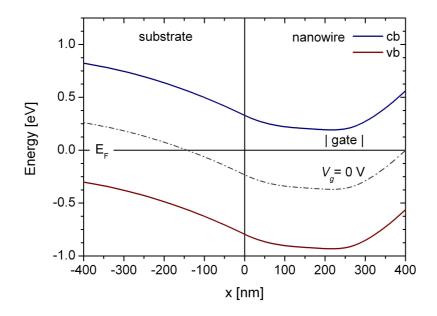

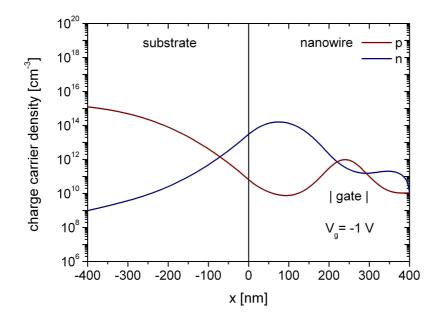

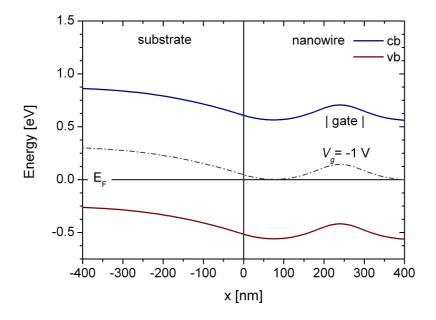

After these partially theoretical considerations with regard to the nanowire morphol-

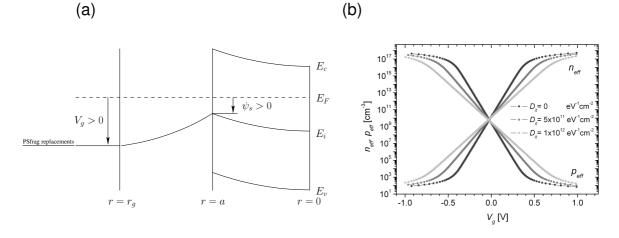

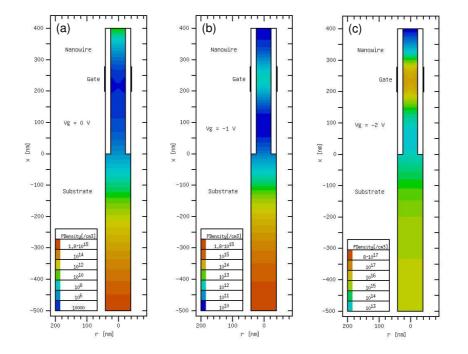

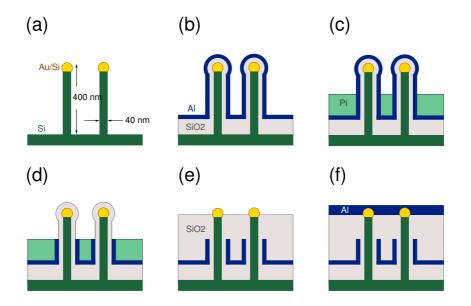

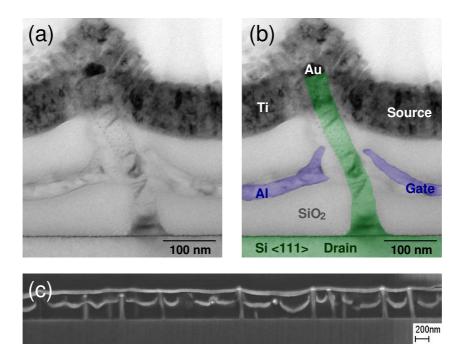

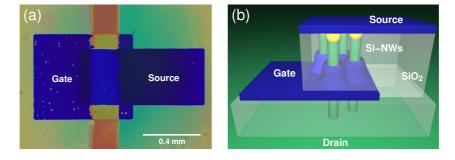

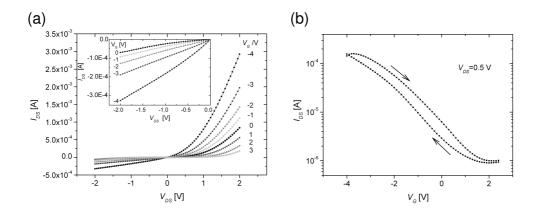

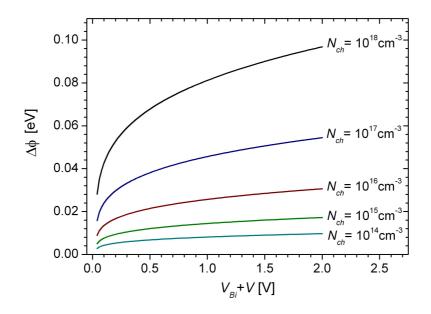

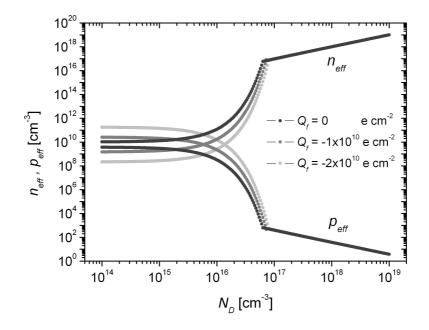

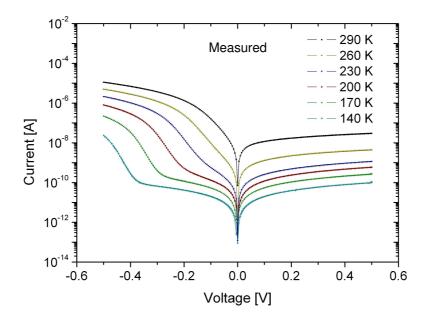

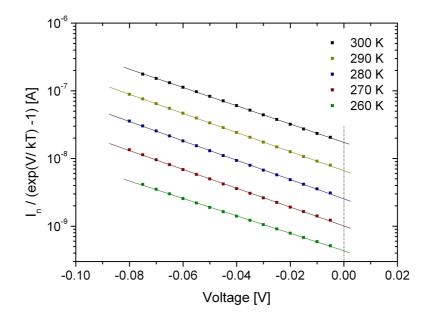

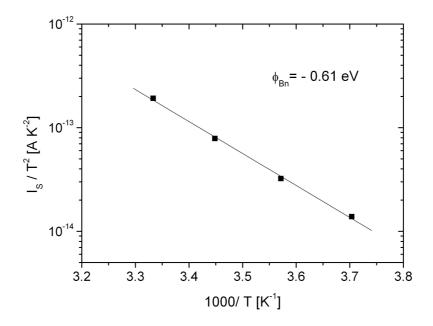

ogy, the electrical properties of silicon nanowires will be subject of Chapter 5. In the beginning of this chapter we will derive a model for the dependence of the charge carrier density of a silicon nanowire on the density of interface traps and interface charges located at the  $Si/SiO_2$  interface. Subsequently, temperature-dependent electrical measurements of both p-doped and n-doped silicon nanowires are presented and discussed in detail. It will be seen that indeed the influence of interface traps and interface charges on the electrical properties can not be neglected. To some degree, the electrical characterization described in Chapter 5 may be seen as a preparatory work for Chapter 6. Having electronic applications of silicon nanowires in mind, the fabrication of a silicon nanowire field-effect transistor is naturally the first step. In this context, epitaxially grown silicon nanowires offer the decisive advantage that, owing to the vertical arrangement of the nanowires, a transistor gate can be wrapped around the silicon nanowire. In Chapter 6 we will present a process flow for the fabrication of an array of vertical surround-gate field-effect transistors out of epitaxially grown silicon nanowires. The feasibility of the fabrication process and the basic functionality of the devices is at last demonstrated by an electrical characterization of such an array of silicon nanowire surround-gate field-effect transistors.

For the convenience of the reader, magnified versions of all graphs are reproduced in the appendix.

# Contents

| Pr                      | eface |                                                                   | ii |  |

|-------------------------|-------|-------------------------------------------------------------------|----|--|

| Introduction and Survey |       |                                                                   |    |  |

|                         | I.1   | Vapor-Liquid-Solid Growth Mechanism                               | 1  |  |

|                         | I.2   | Different Growth Methods                                          | 4  |  |

|                         | I.3   | Silicon Nanowire Heterostructures                                 | 7  |  |

|                         | I.4   | Doping and Electrical Properties                                  | 8  |  |

| 1                       | Silic | on Nanowire Growth                                                | 11 |  |

|                         | 1.1   | Wafer Preparation                                                 | 11 |  |

|                         | 1.2   | Experimental Setup                                                | 12 |  |

|                         | 1.3   | Catalyst Deposition and Annealing                                 | 13 |  |

|                         | 1.4   | Experimental Results Using Gold as Catalyst                       | 15 |  |

|                         | 1.5   | Using other Catalysts than Gold                                   | 17 |  |

|                         |       | 1.5.1 Palladium                                                   | 18 |  |

|                         |       | 1.5.2 Iron                                                        | 19 |  |

|                         |       | 1.5.3 Dysprosium                                                  | 20 |  |

|                         |       | 1.5.4 Bismuth                                                     | 21 |  |

|                         |       | 1.5.5 Indium                                                      | 22 |  |

|                         |       | 1.5.6 Aluminum                                                    | 22 |  |

|                         | 1.6   | Conclusions of Chapter 1                                          | 24 |  |

| 2                       | Diar  | neter Dependence of the Growth Velocity                           | 25 |  |

|                         | 2.1   | Introduction                                                      | 26 |  |

|                         | 2.2   | Definitions and Experimental Results                              | 27 |  |

|                         | 2.3   | Theoretical Model                                                 | 29 |  |

|                         | 2.4   | Conclusions of Chapter 2                                          | 35 |  |

| 3                       | Exp   | ansion of the Nanowire Base and the Influence of the Line Tension | 36 |  |

|                         | 3.1   | Introduction                                                      | 36 |  |

|                         | 3.2   | Surface Thermodynamics                                            | 37 |  |

|                         | 3.3   | Quasi-static Growth Model                                         | 40 |  |

|                         | 3.4   | Results and Discussion                                            | 41 |  |

|                 | 3.5  | Conclusions of Chapter 3                     | 45 |  |

|-----------------|------|----------------------------------------------|----|--|

| 4               | Diar | neter Dependence of the Growth Direction     | 46 |  |

|                 | 4.1  | Introduction                                 | 46 |  |

|                 | 4.2  | Results and Discussion                       | 47 |  |

|                 | 4.3  | Theoretical Model                            | 49 |  |

|                 | 4.4  | Conclusions of Chapter 4                     | 52 |  |

| 5               | Elec | trical Characterization of Silicon Nanowires | 53 |  |

|                 | 5.1  | Theory                                       | 53 |  |

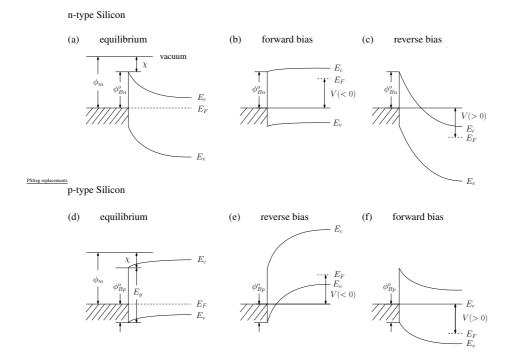

|                 |      | 5.1.1 Metal-Semiconductor Contacts           | 53 |  |

|                 |      | 5.1.2 Silicon/Silicon Dioxide Interface      | 57 |  |

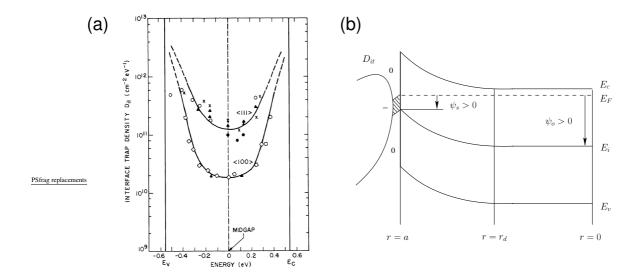

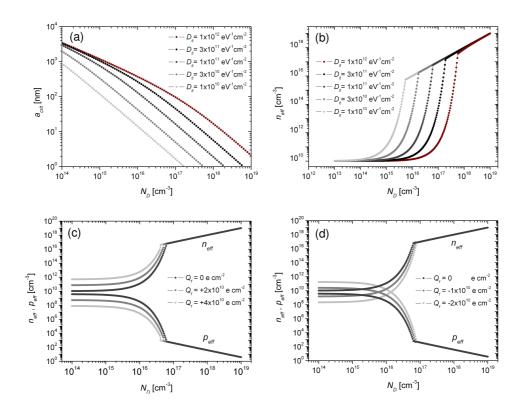

|                 | 5.2  | Array of n-Doped Nanowires                   | 63 |  |

|                 |      | 5.2.1 Experimental                           | 64 |  |

|                 |      | 5.2.2 Results and Discussion                 | 65 |  |

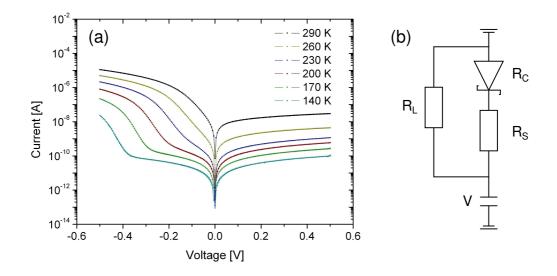

|                 | 5.3  | Array of p-Doped Nanowires                   | 71 |  |

|                 |      | 5.3.1 Experimental                           | 71 |  |

|                 |      | 5.3.2 Results and Discussion                 | 71 |  |

|                 | 5.4  | Conclusions of Chapter 5                     | 75 |  |

| 6               | Vert | ical Surround-Gate Field-Effect Transistor   | 77 |  |

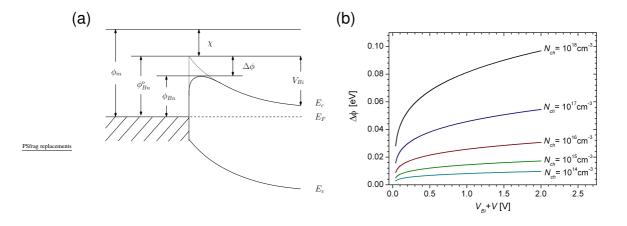

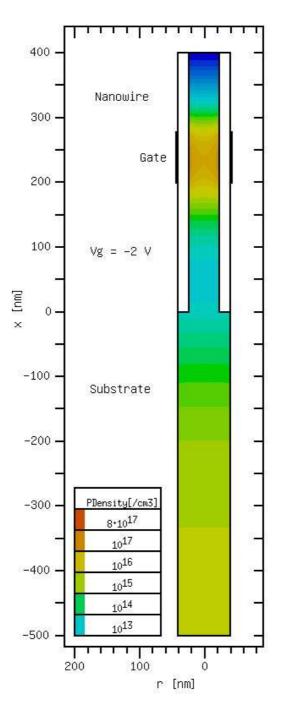

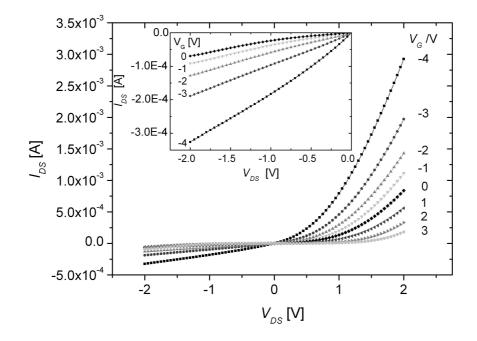

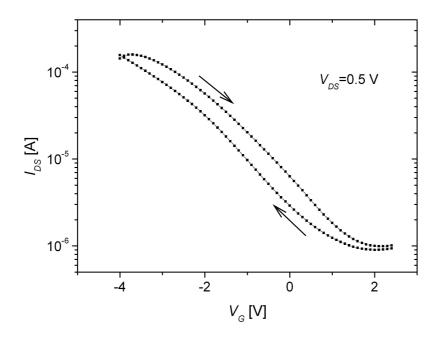

|                 | 6.1  | Theory and Simulation                        | 77 |  |

|                 |      | 6.1.1 MOS Capacitor                          | 78 |  |

|                 |      | 6.1.2 VS-FET Simulation                      | 80 |  |

|                 | 6.2  | Experimental                                 | 82 |  |

|                 |      | 6.2.1 Nanowire Growth                        | 82 |  |

|                 |      | 6.2.2 VS-FET Manufacturing                   | 83 |  |

|                 | 6.3  | Results and Discussion                       | 84 |  |

|                 | 6.4  | Conclusions of Chapter 6                     | 86 |  |

| Summary         |      |                                              |    |  |

| Bibliography    |      |                                              |    |  |

| Appendix        |      |                                              |    |  |

| Acknowledgement |      |                                              |    |  |

## **Introduction and Survey**

Recently, silicon nanowires experienced a considerable increase in attention, with the number of publications in this field doubling about every two years. This renewed interest in silicon nanowires is so much the more a noteworthy fact as the first report on artificial silicon fiber growth by Treuting and Arnold [Tre57] dates back to almost five decades ago. Moreover it is most remarkable that their result concerning the crystallographic growth direction of the silicon filamentary crystals, called whiskers at that time, is still valid, even for most of the silicon nanowires synthesized nowadays. However, before going deeper into the subject, it shall be plainly stated here that a silicon wire is defined as a rod-like silicon structure having a length that considerably exceeds its diameter. Silicon wires with diameters in the nanometer range will be referred to as silicon nanowires. These definitions, though not applied too strictly, will be adopted throughout this thesis.

In the early years of silicon wire research, the growth mechanism leading to the unidirectional silicon wire growth was still under discussion, when in 1964, R. S. Wagner and W. C. Ellis [Wag64a] in a pioneering publication proposed the vapor-liquid-solid (VLS) mechanism of crystal growth. At least for the growth of silicon wires and nanowires, where it is still the most prominent synthesis technique, the validity of the vapor-liquid-solid growth mechanism is widely accepted. The validity range of the vapor-liquid-solid mechanism is astonishingly broad, as wires with diameters from a few nanometers up to a few hundred micrometers can be synthesized via the vapor-liquid-solid growth mechanism. Although this mechanism applies to a much broader range of synthesis methods, it will be discussed exemplarily on the basis of the chemical vapor deposition of silicon wires using silane as precursor gas and gold as catalyst.

#### I.1 Vapor-Liquid-Solid Growth Mechanism

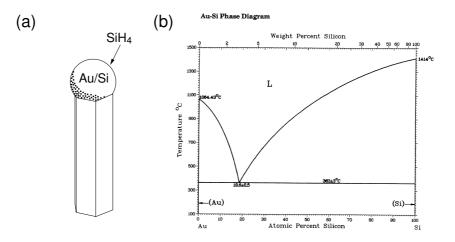

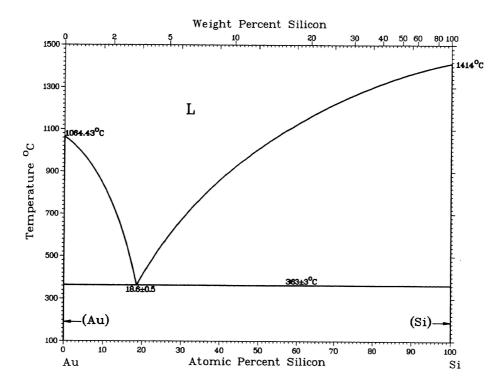

It has been observed experimentally, that the addition of a catalyst metal, like gold for example, strongly enhances the growth of silicon wires. As schematically shown in Fig.I.1(a), silicon wires grown with the help of gold usually exhibit a Au/Si alloy particle at their tip, and it is this Au/Si alloy particle that plays the central part in the model of Wagner and Ellis. The Au/Si phase diagram, displayed in Fig. I.1(b), is of the simple eutectic type; dominated by a low temperature eutectic point at 363 °C [Mas90a]. Hence at temperatures above the eutectic temperature the Au/Si alloy particle transforms into a liquid droplet of a composition that approximately corresponds to the silicon rich branch of the Au/Si phase

Figure I.1: (a) Schematic depicting the vapor-liquid-solid nanowire growth. (b) Au-Si phase diagram [Mas90a], see also Fig. A.1.

diagram, shown in Fig. I.1(b). During growth, silicon is supplied via the gaseous silicon precursor, silane. The silane molecules from the vapor phase are adsorbed on the droplet surface and cracked into silicon and hydrogen [Hog36].

$$\operatorname{SiH}_4 \to \operatorname{Si} + 2 \operatorname{H}_2$$

. (I.1)

After the incorporation of the silicon atoms, resulting from the chemical reaction at the droplet surface, the silicon atoms diffuse through the droplet to the liquid-solid interface, separating the metal alloy droplet from the silicon wire. Under growth conditions, the silicon concentration in the droplet is higher than the equilibrium concentration at this temperature, which is equivalent to a silicon chemical potential in the liquid  $\mu^l$  that exceeds the chemical potential of the silicon nanowire  $\mu^s$ . The droplet is then said to be supersaturated, where

$$\Delta \mu = \mu^l - \mu^s \,. \tag{I.1}$$

defines the silicon supersaturation  $\Delta \mu$  [Giv87a]. The supersaturation of the Au/Si alloy droplet represents the driving force for the growth of the silicon wire.

Thus the vapor-liquid-solid mechanism of silicon wire growth basically consists of three steps: first, the adsorption and cracking of the gaseous silicon precursor, providing atomic silicon for the growth, followed by the incorporation of silicon atoms into the droplet; second, the diffusion of the silicon atoms through the droplet; and third, the condensation of silicon onto the silicon wire at the liquid-solid interface. The question, which of these three steps effectively determines the silicon wire growth rate was controversially discussed. It was only agreed upon that the diffusion step can not be rate determining, since the diffusion through the liquid alloy droplet is simply too fast [Giv87b]. Concerning the other two steps, Bootsma and Gassen [Boo71] favored step one, whereas Givargizov [Giv87b] took the opinion that the condensation of silicon onto the nanowire at the liquid-silicon interface is rate determining. Concerning this discussion, it must however be clear that under steady state growth conditions the incorporation rate has to equal the condensation rate, which requires some kind of interaction between both processes. Thus they can not be dealt as independent processes, and a discussion whether in general one step or the other is rate determining over-simplifies the problem. A general description, therefore, has to consider both processes, such that a situation where in fact one process is rate determining can be discussed as a special limit of the general solution.

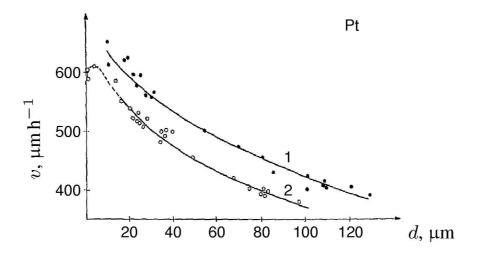

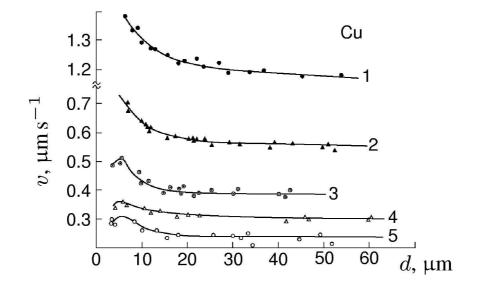

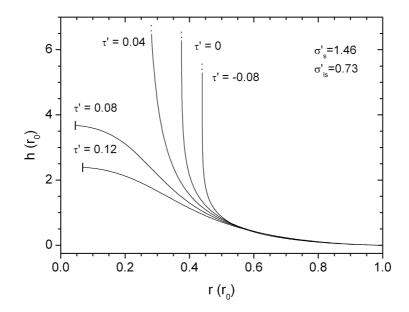

One somehow related issue in this context is the radius dependence of the growth velocity. Considering the surface contribution of the energy of the droplet, the chemical potential of the silicon wire is rendered by an additional radius-dependent term. This is usually referred to as the Gibbs-Thomson effect. As a consequence, also the supersaturation of the droplet, defined in equation (I.1), becomes radius-dependent. Since the supersaturation is the driving force for the silicon wire growth, this implies a radius dependence of the growth velocity. However, here things start to become more complex, as some silicon wire growth experiments indicate an increase of the growth velocity with increasing wire radius [Giv75], whereas others [Wey78, Neb05] show a decrease of the growth velocity with increasing radius. How this riddle can be solved will be subject of Chapter 2, where we present a model considering the interplay of the incorporation and the condensation step under steady state conditions. We will see that both steps can not be dealt independently of each other, and that it is indeed the interplay of both steps that determines the growth velocity.

In the vapor-liquid-solid growth mechanism, the properties of the droplet surface play an important role for the unidirectionality of the silicon wire growth. In general, the droplet surface is assumed to be ideally rough, such that all the impinging vapor molecules are captured. At least for silane as vapor phase silicon source, the adsorption and cracking efficiency of the Au/Si droplet surface is significantly higher than the adsorption and cracking efficiency of the pure silicon surface. This important property of the droplet surface, i.e. the high adsorption and cracking efficiency, is usually referred to as the catalytic ability of the Au/Si droplet. However, as pointed out by Givargizov [Giv87b], speaking of catalytic ability is somehow misleading in this context, as it does not imply a catalysis of the silane reaction in a chemical sense. The so-called catalytic ability of the droplet more relates to the high sticking coefficient of the droplet with respect to the precursor gas [Wag65]. By measuring the axial and radial wire growth rates, Bootsma and Gassen [Boo71] could determine that under their growth conditions, the adsorption and cracking efficiency of the droplet is roughly three orders of magnitude higher than the corresponding efficiency of the silicon surface. To conclude, the high adsorption and cracking efficiency of the Au/Si droplet surface, compared to the corresponding efficiency of the silicon surface, leads to the growth of silicon wires with almost constant radius.

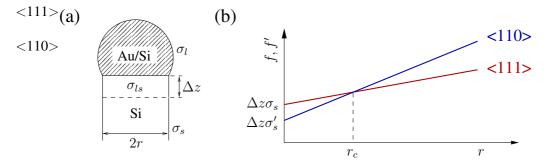

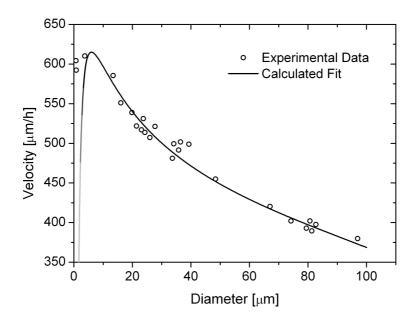

Taking wire growth via the vapor-liquid-solid mechanism into account, it becomes immediately clear that the radius r of the wire is directly related to the radius R of the droplet. Considering the situation where a droplet in thermal equilibrium is sitting on top of a cylindrical silicon rod, additionally assuming a flat interface, the radius r of the wire

is determined by the droplet radius R

$$r = R \sqrt{1 - \left(\frac{\sigma_{ls}}{\sigma_l}\right)^2} \qquad [\text{Neb03}]. \tag{I.1}$$

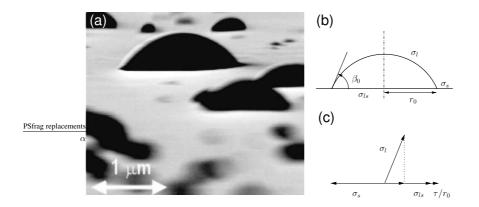

Here  $\sigma_{ls}$  and  $\sigma_l$  denote the liquid-solid interface tension and the liquid surface tension  $\sigma_l$  of the droplet. Thus the radius of the Au/Si catalyst droplet is larger than the radius of the wire, which was taken to be constant for now. This however, does not hold for the initial growth stage of silicon wires, grown epitaxially on a silicon substrate. They exhibit a strong expansion in the region where the wire is attached to the substrate (see e.g. [Wag67]). As pointed out by Givargizov [Giv87c], this expansion, however, is not related to an overgrowth of the silicon wire caused by a direct deposition of silicon atoms on the nanowire flanks. As discussed in detail in Chapter 3, this phenomenon can be explained by a change of the droplet shape in the initial growth stage [Shc90, Neb96, Sch05c].

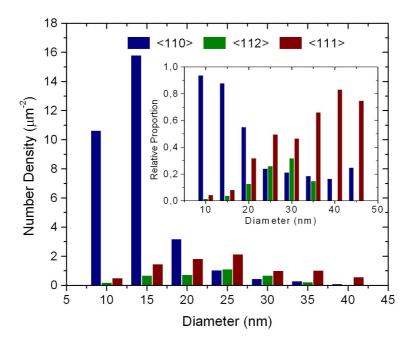

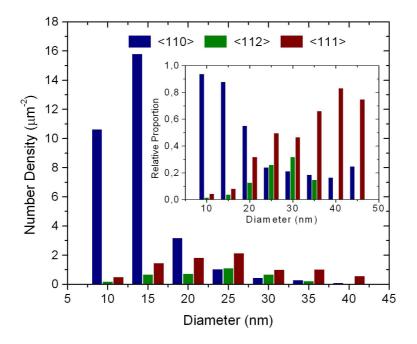

Silicon wires synthesized using gold as catalyst are in general single crystalline, although sometimes crystallographic defects like stacking faults or dislocations are observed [Wag67]. Experimental results indicate that the crystallographic growth direction of silicon nanowires grown with gold is diameter dependent [Wu04a, Sch05a]. For large diameters, greater than about 50 nm, the nanowires tend to grow in a <111> direction. This is, by the way, the most often reported silicon wire growth direction. In addition to the <111> direction also the <110> and <112> growth directions are observed, especially for diameters smaller than about 50 nm. The diameter dependence of the growth direction is discussed in detail in Chapter 4, where also a model for this direction change is proposed.

#### I.2 Growth Methods and Catalyst Materials

Several methods for the synthesis of silicon nanowires have been established in the last fifty years. These methods mainly differ with respect to the catalyst material used and with respect to the means by which the silicon is supplied. Concerning the silicon supply, the most popular method seems to be the chemical vapor deposition (CVD) using a gaseous silicon precursor like silane, SiH<sub>4</sub> [Boo71, Wes97a, Wes97b], silicon tetrachloride, SiCl<sub>4</sub> [Wag64a, Giv71, Hoc05], or silicon diiodide, SiI<sub>2</sub> [Gre61, Wag61]. Also disilane, Si<sub>2</sub>H<sub>6</sub> [Han06], is sometimes used; especially if low pressure growth conditions are desired. In order to enhance the effectiveness of the chemical vapor deposition at low temperatures for example, a plasma might be used to pre-crack the silicon precursor and to facilitate thereby the growth of the silicon nanowires [Hof03, Zen03]. Also strong electric fields were shown to influence the growth of silicon nanowires [Che03, Eng05]. Another prominent synthesis approach is based on the thermal evaporation of silicon monoxide, SiO. At elevated temperatures SiO decomposes at the silicon nanowire tip into Si and SiO<sub>2</sub>, leading to the formation of silicon nanowires that are usually covered by a thick silicon oxide shell. Concerning silicon nanowire growth via SiO decomposition, both growth via the vapor-liquid-solid mechanism [Kol04] as well as catalyst-free growth [Zha99] has been reported in literature. Other silicon nanowire synthesis methods mostly rely on the direct <sub>[Lev70]</sub>evaporation of silicon. This can either be achieved with the help of a molecular beam epitaxy (MBE) system [Sch04, Fuh05], by simple thermal evaporation [Fen00], or by means of laser ablation [Mor98, Bar02].

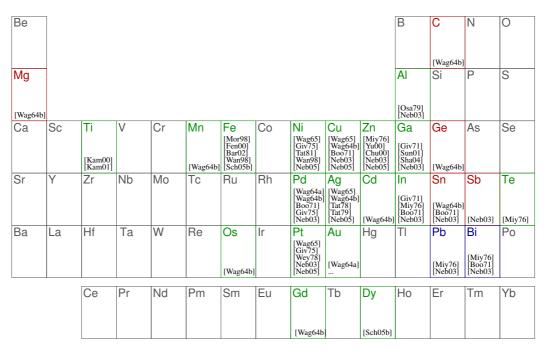

Regarding the catalyst materials, a large number of different materials has been tested for their ability to catalyze silicon wire growth. Figure I.2 displays a table of the elements that have been tested so far, giving also the corresponding literature references. The elements in green framed boxes are reported to promote silicon wire growth, whereas the elements in red framed boxes have been tested unsuccessfully. Concerning the elements in blue framed boxes, the reports in literature are somewhat controversal.

Figure I.2: Table of elements tested with regard to their ability of catalyzing silicon nanowire growth; green box: successful, red boxes: unsuccessful, blue boxes: controversal reports

Besides gold, the first elements that were reported as catalyst materials for silicon wire growth are the elements nickel, copper, palladium, silver, and platinum [Wag64a]. The resulting silicon wires, synthesized at temperatures between  $850 \,^{\circ}$ C and  $1050 \,^{\circ}$ C in a CVD process using SiCl<sub>4</sub>, show large similarities with the wires obtained with gold as catalyst. They are almost constant in diameter and exhibit a globular catalyst particle at their tip. In addition, they are single crystalline and mostly <111> oriented. The main disadvantage of these catalysts is, however, that a low temperature vapor-liquid-solid growth, like in case of gold, is not possible for the above mentioned metals. The melting points of the corresponding metal/Si alloys are in all cases above  $800 \,^{\circ}$ C.

Other possible catalyst materials for the chemical vapor deposition of silicon nanowires are the group III elements indium and gallium. The Ga/Si and In/Si phase diagrams are very similar. Both are of the simple eutectic type, with a eutectic point at very low temperatures of 30 °C and 157 °C, respectively. So from this point of view it is not too astonishing that silicon nanowire growth experiments using gallium or indium as catalyst provide similar results [Giv71]. Although a vapor-liquid-solid growth of silicon nanowires using gallium or indium is possible, it appears to be more difficult than for nickel, copper, or the precious metals. Moreover, the wires grown at high temperatures using gallium and indium are strongly tapered [Giv71]. This might be related to the loss of the catalyst material during growth, either by incorporation of the catalyst material into the silicon wire or by loss through a volatile reaction product. Another explanation for the tapering is provided by Nebolsin et al. [Neb03]. According to their model, a stable vapor-liquid-solid growth of nanowires having a constant diameter requires that the surface tension of the liquid droplet,  $\sigma_l$ , is greater than  $\sigma_s/\sqrt{2}$ ; with  $\sigma_s$  being the silicon surface tension. This criterion for the growth of cylindrical silicon nanowires is not met by gallium and indium, which might be a possible explanation for the tapering of the wires. A different route for the synthesis of silicon nanowires using gallium as catalyst was followed by Sunkara et al. [Sun01], who demonstrated the synthesis of polycrystalline silicon nanowires by a plasma enhanced chemical vapor deposition (PECVD) process. To this end, 700 W of microwave power and a substrate temperature around  $450 \,^{\circ}$ C were applied to a gallium covered silicon substrate in hydrogen atmosphere. With the help of the hydrogen plasma, volatile silicon compounds were produced, which served as vapor phase source for the growth of the silicon nanowires. Silicon nanowires of higher crystalline quality were produced in a similar PECVD process by Sharma et al. [Sha04] at slightly higher temperatures (550  $^{\circ}$ C), with the only difference that silane was used as vapor phase silicon source.

Similar to gallium and indium, the Zn/Si phase diagram exhibits a single eutectic point at moderate temperature (420 °C). According to Yu et al. [Yu00], who report on silicon nanowire growth with zinc as catalyst, a vapor-liquid-solid growth using diluted silane (5% in Ar) is possible at temperatures between 450 °C and 500 °C. Silicon nanowires with diameters down to 10 nm could be produced this way. They found two types of nanowires: <111> and <112> oriented ones, both of them single crystalline, with few crystallographic defects.

One of the most promising elements for vapor-liquid-solid silicon nanowire growth seems to be aluminum. The Al/Si phase diagram shows the closest similarities with the Au/Si phase diagram. It exhibits a single eutectic point at a temperature and a silicon concentration comparable to the eutectic point of the Au/Si phase diagram. However, only little is reported on the growth of silicon nanowires with the help of aluminum. Our own results, presented in Section 1.5 indicate that silicon nanowires grown with the help of aluminum tend to be stronger facetted and tapered than nanowires grown with gold as catalyst. However, recent results show that the tapering of the wire can be strongly reduced by optimizing the growth parameters. The resulting wires obtained with aluminum as catalyst are in general single crystalline with few crystallographic defects.

An element which seems to work well, though at extremely high temperatures, is iron. The lowest melting point of the Fe/Si phase diagram is at 1207 °C, and correspondingly high temperatures have to be applied for a vapor-liquid-solid silicon nanowire growth.

Morales et al. [Mor98] first demonstrated the laser assisted synthesis of silicon nanowires with iron as catalyst. With the help of a frequency doubled Nd:YAG laser they ablated silicon and iron from a Si:Fe (9:1) target mounted in a quartz oven that was heated to 1200 °C and filled with 0.5 bar of argon. Owing to the high argon background pressure, the ablated iron and silicon atoms could collide and react in the vapor phase, which then led to the growth of single crystalline, <111> oriented silicon nanowires. Similar results were obtained by Feng et al. [Fen00] by simply heating a Si:Fe (19:1) target at 1200 °C for twenty hours in an argon filled quartz oven. As presented in Section 1.5, iron can also be used for silicon nanowire growth at temperatures far below the melting point of the alloy, although the crystalline quality of the nanowires obtained that way is poor [Sch05b]. It seems probable that in this case, a solid iron silicide particle is responsible for the nanowire nucleation. Thus growth would proceed via a vapor-solid-solid mechanism. Such a vapor-solid-solid growth of silicon nanowires can also be observed if titanium [Kam00] or dysprosium [Sch05b] are used instead of iron, and growth temperatures below the melting point of the corresponding alloy are applied.

The group IV and V elements germanium, tin, lead, and bismuth do not seem to promote silicon nanowire growth [Neb03, Boo71], although Miyamoto [Miy76] reports on the growth of amorphous silicon nanowires using bismuth and lead. Concerning the remaining elements magnesium, manganese, gadolinium, osmium, and tellurium only little information is available [Wag64b, Miy76]. It is reported that, with the exception of magnesium, the latter elements do promote silicon nanowire growth [Wag64b, Miy76].

#### I.3 Silicon Nanowire Heterostructures

Semiconductor heterostructures in general offer interesting perspectives for electronic and optoelectronic devices. For two reasons semiconductor nanowires are very attractive for this aim. The first is that semiconductor nanowires offer the possibility of epitaxially combining materials with a large lattice misfit. If two bulk materials having a lattice misfit are brought together in the form of a thin film of one of the materials on top of the other, the strain in the material, caused by the lattice misfit at the heterojunction, is reduced by the creation of misfit dislocations if a certain critical layer thickness is exceeded. These dislocations have detrimental influence on the electrical and optical properties. However, a semiconductor nanowire of sufficiently small radius can react elastically to the stress caused by the lattice misfit, without producing dislocations [Ert03, Käs04]. The second advantage of semiconductor nanowires with respect to the synthesis of heterostructures is the intrinsic radial confinement of the charge carriers in the nanowire. Owing to this radial confinement, three-dimensional quantum dots can be produced in a relatively simple way. This has, for example, been demonstrated by Björk et al. [Bjö02] for an InAs/InP nanowire heterostructure. The electronic properties of this heterostructure have been calculated by Zervos et al. [Zer04].

With respect to silicon nanowire heterostructures, a combination of silicon with the other group IV semiconductor, germanium, seems to be the natural choice. Especially, as

a perfect Si/Ge superlattice offers the interesting perspective that the combined material might develop a direct band gap [Pre92]. However, there have only been few reports on axial Si/Ge heterostructure wires. Givargizov et al. demonstrated in an early work [Giv71] the synthesis of Si/Ge heterostructure wires produced by chemical vapor deposition using SiCl<sub>4</sub> and GeCl<sub>4</sub> as precursors. In a more recent work, Wu et al. [Wu02] were able to produce Si/SiGe heterostructure nanowires by a hybrid approach combining chemical vapor deposition with pulsed laser deposition. In their experiments, SiCl<sub>4</sub> was used as gaseous silicon source. The germanium was supplied by ablating a germanium target using a pulsed Nd:YAG laser.

Also radial heterostructures offer interesting opportunities, especially with regard to electronic applications. Covering a nanowire with a shell material, having a larger band gap, would confine the charge carriers to the core of the nanowire heterostructure. This might be an interesting route to reduce the surface scattering of the charge carriers, for example. In addition, the energetic alignment of different band gap materials might be used to alter the electronic properties of core and shell, and to circumvent this way the problem of doping.

The synthesis of epitaxial Si/Ge, Ge/Si, and Si/Ge/Si core-shell and core-multishell heterostructure nanowires, respectively, has been demonstrated by Lauhon et al. [Lau02]. In a first step they synthesized silicon or germanium nanowires via a CVD process using silane and germane as precursors and gold as catalyst. The shell material was subsequently deposited at temperatures below the Au/Si or Au/Ge eutectic point, and annealed afterwards. Their electrical characterization of a p-Si/i-Ge/SiO<sub>x</sub>/p-Ge heterostructure revealed a promising performance characteristic, with a transconductance of  $1.5 \,\mu A V^{-1}$ .

Aiming more at optoelectronic applications, Hayden et al. [Hay05] were able to produce a Si/CdSe core-shell heterostructure nanowire that functioned as a light emitting diode. For this purpose, single crystalline p-type silicon nanowires, grown in a CVD process using gold as catalyst were covered with an n-type polycrystalline CdSe shell by pulsed laser deposition. By separately contacting core and shell of a single nanowire and applying a voltage across the pn-junction, an electroluminescence signal with a peak at 528 nm could be produced.

#### I.4 Doping and Electrical Properties

One issue that has not been addressed so far is the question of wanted and unwanted impurities in silicon nanowires. As practically all semiconductor devices rely on a controlled doping of the semiconductor material, clearly, a both quantitatively and spatially controlled doping of the silicon nanowire is desirable. In principle, the vapor-liquid-solid growth mechanism offers two possible routes to dope silicon nanowires. The easiest way, at least from a technical point of view, is to vaccinate the Au/Si droplet with the dopant prior to growth, i.e. to grow the nanowires with a Au/Si/dopant mixture as catalyst. Cui et al. [Cui00] demonstrated silicon nanowire synthesis with the help of a 200:1 Au:P mixture. They electrically characterized the thereby obtained nanowires by placing sin-

gle nanowires on an oxidized silicon substrate and contacting them with the help of an e-beam lithography system. They performed two-terminal measurements on the contacted nanowires, additionally using the oxidized silicon substrate as a back-gate, by which they applied a gate voltage. Measuring the gate voltage dependence they were able to show that the phosphorus-doped silicon nanowires indeed behaved like highly n-doped silicon rods. The resistivity of heavily phosphorus-doped silicon nanowires was found to be as low as  $0.023 \Omega$  cm.

The more advanced alternative doping method is to add a small amount of a gaseous dopant precursor, like phosphine, PH<sub>3</sub>, or diborane, B<sub>2</sub>H<sub>6</sub>, to the gaseous silicon precursor. This theoretically offers the possibility of varying the doping of the nanowires during growth, by changing the partial pressure of the corresponding dopant gas. However, sharp transitions between differently doped nanowire regions seem hard to achieve experimentally, since the Au/Si droplet might act as a reservoir for the dopant atoms. Cui et al. [Cui00] also characterized boron doped silicon nanowires that were grown by chemical vapor deposition using silane as silicon source and diborane as dopant gas. The SiH<sub>4</sub>:B<sub>2</sub>H<sub>6</sub> ratio was varied between 1000:1 and 2:1. The low doped silicon nanowires showed a resistivity of  $390\,\Omega$  cm, whereas the silicon nanowire grown with a silane to diborane ratio of 2:1 exhibited almost metallic behavior with a resistivity of  $0.007 \,\Omega$  cm. From gate voltage dependend measurements they determined a carrier mobility of  $3 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for the heavily doped nanowires. Wu et al. [Wu04b] report a mobility of  $325 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for medium boron-doped nanowires, which is a mobility value comparable to that of bulk silicon. Zheng et al. [Zhe04] fabricated n-doped silicon nanowires doped with phosphine as the dopant source at a silane to phosphine ratio between 4000:1 and 500:1. The electrical characterization was performed as described before, by contacting a nanowire placed on an oxidized silicon substrate. Gate voltage dependent measurements revealed a mobility of  $260 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for the lightly and  $95 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for the heavily doped silicon nanowires, respectively. Nebolsin et al. [Neb95] determined the resistivity of silicon wires grown with gold, nickel, platinum, and copper as catalyst. For all four metals the resistivity at room temperature was found to be of the order of  $10^3 \Omega$  cm, which is about the value of intrinsic silicon. An electrical characterization of undoped silicon nanowires grown with gold and zinc as catalysts was performed by Chung et al. [Chu00] and Yu et al. [Yu00]. They found that both kinds of nanowires are p-type with a resistivity of  $10^5 \,\Omega$  cm for the Zn-catalyzed and  $> 10^3 \Omega$  cm for the Au-catalyzed wires. To conclude, the electrical measurements prove the possibility of doping silicon nanowires either using gaseous dopant precursors or by directly adding the dopant to the catalyst droplet prior to growth. The measured electrical properties are in overall compliance with the properties of bulk silicon.

Another important issue are unwanted impurities in the silicon nanowire caused by the presence of the catalyst droplet itself. Especially for gold this is critical as gold is known to create a very effective recombination center in silicon [Lan80]. Although this issue was first brought up more than 40 years ago [Tho66], the question how much gold is typically dissolved in the silicon nanowire, grown at low temperatures, has still not yet been satisfactorily answered. As a comparison, the analysis of InAs nanowires using a local electrode atom probe microscope revealed an extremely high gold concentration of the order of  $1 \times 10^{18}$  cm<sup>-3</sup> in the InAs nanowire [Per06]. Shchetinin et al. [Shc91] have determined a gold concentration of  $3.5 \times 10^{19}$  cm<sup>-3</sup> in silicon wires grown at 1097 °C by performing local electron-probe microanalysis. Such a concentration would exceed the equilibrium concentration of gold in silicon at this temperature by about two orders of magnitude [Sze81a]. If also at low growth temperatures the gold concentration in silicon nanowires would exceed its equilibrium value by two orders of magnitude, a replacement of gold by an alternative catalyst material may become unavoidable.

### **Chapter 1**

### **Silicon Nanowire Growth**

In this chapter our experimental results on the growth of silicon nanowires will be presented. We begin with the description of the wafer cleaning procedure, the experimental setup and the growth process. Afterwards, the epitaxial growth of silicon nanowires on silicon substrates using gold as catalyst is demonstrated. Our experimental results, using other catalyst materials than gold, are discussed subsequently.

#### **1.1 Wafer Preparation**

Before we come to the silicon nanowire growth itself, shortly the wafer preparation is to be described. In most cases, low doped, <111> oriented 100 mm silicon wafers are used as substrates. Prior to growth, the residual contamination of these wafers is reduced by a two-step wet chemical cleaning process. In preparation of the wafer cleaning, first the necessary equipment is cleaned. For this purpose, two wafer holders and the tweezers are placed inside a quartz bowl and carefully rinsed with high purity water. The quartz bowl is then filled with the RCA1 solution [Ker93] consisting of 21 of high purity water, 200 ml of NH<sub>4</sub>OH, and 400 ml of  $H_2O_2$ , both of very-large-scale integration (VLSI) quality. The cleaning solution is then heated on a hot plate (Schott SLK 2) at maximum power for ten minutes to remove organic contaminations. Care should be taken that the temperature of the solution does not exceed 70  $^{\circ}$ C, since higher temperatures lead to a degradation of the cleaning solution and a concomitant reduction of the cleaning efficiency [Ker93]. After pouring out the RCA1 solution, the quartz bowl and its contents are rinsed again with high purity water. The cleaning procedure is repeated with the RCA2 solution [Ker93], that removes residual metal contaminations. For this aim, the quartz bowl with the holders and the tweezers inside is filled with 1.8 l of high purity water, 300 ml of concentrated HCl, and 300 ml  $H_2O_2$ , both of VLSI quality, and heated on the hot plate at maximum power for ten minutes. After pouring out the RCA2 solution, the bowl, the wafer holders, and the tweezers are rinsed with high purity water. With this, the preparations are completed. The wafers that are to be cleaned, usually eight or twelve, are placed in a wafer holder inside the quartz bowl, and the cleaning procedure is repeated as described before. The wafers are heated for ten minutes in the RCA1 solution, rinsed with high purity water, heated in

the RCA2 solution for ten minutes, and again rinsed with high purity water. To protect the wafers against dust particles from the ambient air, the wafers are kept immersed during and after the cleaning process. The easiest way to remove the native  $SiO_2$  layer of the wafers is to dip the wafers for a few seconds into hydrofluoric acid. For this purpose a Teflon bowl is filled with 1.9 l of high purity water and 100 ml of concentrated HF (50%), corresponding to a concentration of 2.5%. Now a pair of wafers each is dipped for thirty seconds in the diluted HF to obtain an oxide free silicon surface. Together with the removal of the  $SiO_2$ the silicon wafer surface becomes hydrogen terminated and hydrophobic. The wafer pair is then mounted with the polished sides face to face on a spinner, where three spacers keep the wafers at a distance of about 1 mm. The wafer pair is rotated at about 3000 turns/min for a few seconds to remove last HF drops from the wafer surface. Then the spacers are retracted and the wafers are slightly pressed together. If the wafer surfaces are sufficiently clean, this initiates a hydrophobic bonding of the wafers. The advantage of this hydrophobic bonding of the wafers is that from the moment of the bonding on, the cleaned polished surfaces of the wafers are protected against further dust and hydrocarbon contamination. The bonded wafers are then transferred into the UHV system without further delay.

#### **1.2 Experimental Setup**

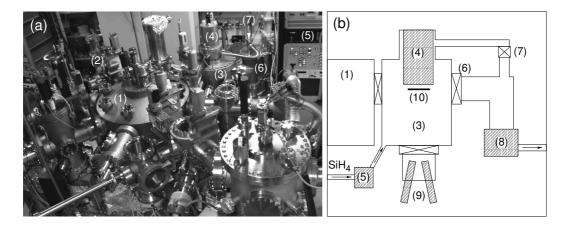

Figure 1.1: (a) Photograph of the UHV system. (b) Schematic side view of the growth chamber. (1) Main chamber, (2) metal deposition chamber, (3) growth chamber, (4) radiative heater, (5) mass-flow controller, (6) main valve, (7) dosing valve, (8) turbo pump, (9) antimony and boron evaporation sources, (10) silicon wafer.

The UHV system Fig. 1.1(a) is a cluster tool, consisting of the main chamber (1), having a base pressure around  $1 \times 10^{-10}$  mbar, and several attached side chambers, designed for different purposes. One of the necessary side-chambers for silicon nanowire growth is the metal deposition chamber (2), in which usually four electron beam evaporation sources (Tectra) are mounted. They are designated to the deposition of different catalyst materials for nanowire growth, as well as to the deposition of backside metal contacts to the silicon wafers. The thickness of the evaporated metal layer can be controlled by a quartz deposition controller (Inficon). After depositing the catalyst metal, gold in most cases, the wafer can be transported in situ to the growth chamber (3). A schematic side view of the growth chamber is shown in Fig. 1.1(b). There the wafer (10) is positioned directly below a radiative heater (4) (Roth + Rau). This heater, designed for 100 mm wafers, basically consists of a graphite coil through which a high current is driven. To achieve a better homogeneity of the radiated heat, a graphite plate is located between the graphite coil and the wafer. The temperature of the heater and the ramping speed are controlled by a PID-controller (Eurotherm 216e). The heater was calibrated using a low doped silicon wafer of standard thickness onto which five thermocouple elements were tightly attached at different distances from the center of the wafer. The flow of diluted silane and other gases into the growth chamber is adjusted by an eight-channel mass flow controller (5) (MKS Instruments 647B). In order to achieve a constant growth pressure during nanowire growth, the main valve (6) that separates the growth chamber from the turbo pump (8) (Pfeiffer Vacuum TMU 520 C) is closed, while the dosing valve (7) is opened just wide enough to keep the pressure constant. The outgoing flow through the dosing valve can be indirectly controlled via the power consumption of the turbo pump (8). As discussed before, a doping of the nanowires can be achieved by mixing a small amount of a dopant metal to the catalyst droplet. For this aim two evaporation sources (9) are mounted right below the growth chamber. Antimony is deposited by an electron beam evaporation source (Tectra), while a thermal high temperature evaporation source (MBE Komponenten, HTS) is used for the boron evaporation.

#### **1.3** Catalyst Deposition and Annealing

After transferring the pre-bonded wafer pairs into the UHV system, the wafers are either stored inside the UHV system at a pressure of  $1 \times 10^{-10}$  mbar or separated in situ for nanowire synthesis. For the deposition of the catalyst material, one wafer is transported into the metal deposition chamber. Usually, a layer, 0.1 nm to 0.5 nm thick, is evaporated onto the hydrogen terminated wafer surface. After the deposition, the wafer is transported in situ to the growth chamber for an annealing of the catalyst metal layer. An annealing of the catalyst is the easiest method to produce a large number of separated catalyst particles, necessary for the nanowire synthesis.

As shown in Fig. I.1(b), the characteristic feature of the Au/Si phase diagram is its low temperature eutectic point at 363 °C, at temperatures significantly lower than the melting points of pure gold, 1064 °C, or pure silicon, 1414 °C. Upon annealing the gold film at a temperature above the eutectic temperature, silicon from the substrate will diffuse into the gold layer, producing a liquid Au/Si alloy. In order to reduce its total surface and interface energy, the Au/Si film will break up into a distribution of Au/Si droplets. In addition to these droplets, a certain density of gold ad-atoms will be present on the silicon surface. These ad-atoms can diffuse on the silicon surface. Since the larger droplets with their smaller surface-to-volume ratio are energetically more favorable than the smaller droplets,

gold ad-atom diffusion will lead to a net transport of gold from the smaller to the larger droplets. Thus the larger droplets will grow at the expense of the smaller ones. This process of particle growth is known as Ostwald ripening. A first theory of Ostwald ripening was developed by Lifshitz and Slyozov [Lif61]; a comprehensive treatment based on their theoretical model was presented by Chakraverty [Cha67] and Wynblatt et al. [Wyn76b, Wyn76a]. The outcome of the model is threefold. First, the existence of a critical timedependent droplet radius  $r^*(t)$  is predicted. At a time t, droplets that are smaller than the critical radius  $r^*(t)$  will shrink, while droplets having a radius greater than  $r^*(t)$  will increase in size. If the transition of gold ad-atoms to or from the droplets is taken to be the rate determining step of the ripening process, the critical radius  $r^* = 8/9 \ \overline{r}$ , with  $\overline{r}$  being the average droplet radius [Wag61]. Second, one can show that the average radius of the distribution will increase as a power law in time

$$\bar{r}(t) = \bar{r}(0) \left(1 + \kappa t\right)^{1/2}$$

[Wag61], (1.1)

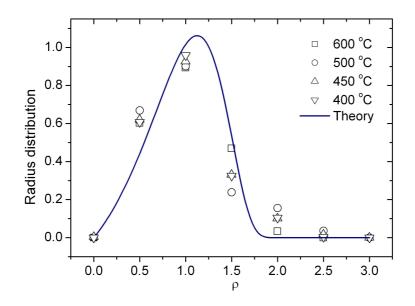

where  $\kappa$  is a kinetic coefficient. The third outcome is that the droplet distribution function  $f(\rho)$ , with  $\rho = r/\bar{r}$ , becomes a time independent function in the limit  $t \to \infty$ . Normalized to unity, the distribution function  $f(\rho)$  is given by [Wag61].

$$f(\rho) = \frac{16\rho}{27(1-\frac{4\rho}{9})^5} \exp\left(\frac{-12\rho}{9-4\rho}\right).$$

(1.2)

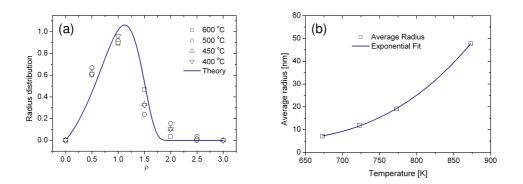

This distribution is plotted in Fig. 1.2(a) as a solid line.

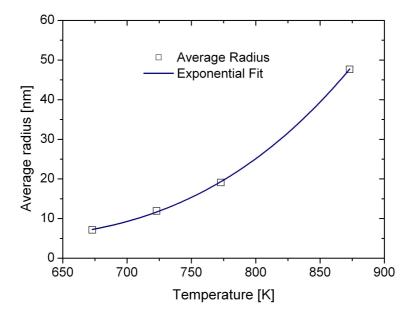

Figure 1.2: (a) Radius distribution of Au/Si droplets after 20 minutes of annealing at different temperatures, see also Fig. A.2. (b) Mean radius of Au/Si droplets as a function of the annealing temperature, see also Fig. A.3.

In order to compare these theoretical predictions with experimental results, we deposited 0.5 nm of gold onto hydrogen-terminated silicon wafers. These wafers were annealed at different temperatures for 20 minutes. At the end of the annealing time the temperature was rapidly decreased. The distribution function was obtained by measuring the droplet radii of overall about two thousand droplets in scanning electron micrographs. The experimentally determined radius distribution is displayed in Fig. 1.2(a). One can see that the theoretical curve is in fair agreement with the experimentally obtained data. Note that the distribution is plotted versus the dimensionless variable  $\rho = r/\bar{r}$  and that this disguises that the mean radius  $\bar{r}$  varies by about a factor of six between the sample annealed at 600 °C and the one annealed at 400 °C.

Figure 1.2 (b) shows the experimentally determined mean radii as a function of temperature and an exponential fit to these data. Suppose, the temperature dependence of the kinetic coefficient  $\kappa$  can be described by an exponential relation with a constant  $\kappa_o$  and an activation energy  $\Delta G$ , then the mean radius  $\bar{r}$  can be expressed as

$$\bar{r}(t,T) = \bar{r}(0) \left(1 + \kappa_o t \exp(-\frac{\Delta G}{kT})\right)^{1/2}.$$

(1.3)

From the least square fit, shown in 1.2 (b), we could obtain the following parameters  $\bar{r}(0) = (5 \pm 1) \text{ nm}$ ,  $\kappa_o = (1.5 \pm 0.4) \times 10^5 \text{ s}^{-1}$ , and  $\Delta G = (1.08 \pm 0.03) \text{ eV}$ . Using these parameters together with equation (1.3) we can estimate the annealing times and annealing temperatures that are necessary to obtain the desired mean droplet radius. Another parameter at hand that can be used for adjusting the droplet size is the initial thickness of the gold film. Thus by varying the initial gold thickness, the annealing temperature, and the annealing time, we are able to adjust both the average droplet size and the droplet density within a certain range.

#### **1.4 Experimental Results Using Gold as Catalyst**

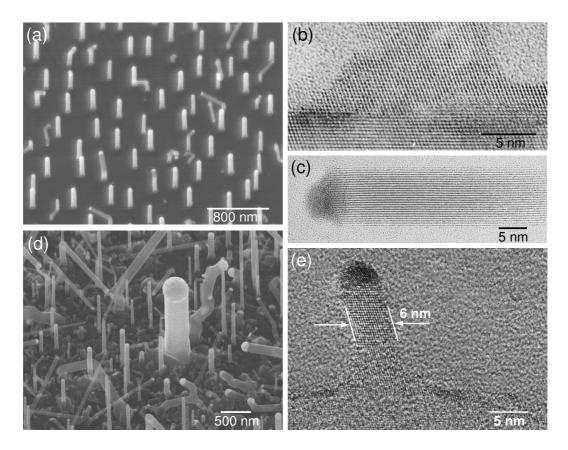

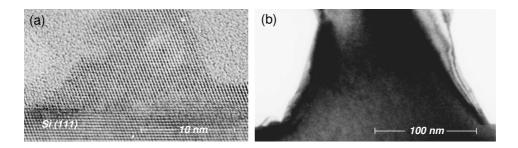

After the annealing of the gold-covered samples, the wafer temperature is lowered to the desired growth temperature, which is usually between 400 °C and 500 °C. The main valve to the turbo pump and the dosing valve are closed, and the growth chamber is filled with diluted silane (5 % in argon) till an overall chamber pressure of about 2 mbar is reached. The silane flow during growth is usually set to 40 sccm. If the desired growth pressure is reached, the dosing valve is slightly opened to establish a constant growth pressure, while maintaining a continuous flow of diluted silane. This state is kept for a few to many minutes. Depending on the growth temperature and pressure the growth velocity varies, but is typically of the order of  $1 \text{ nm s}^{-1}$ . The progress of nanowire growth can be observed through a window of the growth chamber, which is quite helpful, as the visual appearance of the wafer changes considerably during growth. If the desired nanowire length is reached, the silane flow is switched off and the silane remaining in the growth chamber is pumped via the dosing valve, till a chamber pressure of 0.1 mbar is reached. Then the main valve to the turbo pump is opened, which causes a rapid decrease of the chamber pressure to below  $10^{-6}$  mbar. At last, the heating power is reduced and the wafer is cooled down to room temperature. Figure 1.3 (a) shows a scanning electron micrograph of silicon nanowires grown epitaxially on a (111)-oriented substrate. In this experiment 0.5 nm of gold were deposited onto the wafer, and the wafer was annealed at the growth temperature of 450  $^{\circ}$ C for 38 minutes. Silicon nanowire growth proceeded within six minutes, at a chamber pressure of 2 mbar and a flow of 40 sccm of diluted silane (5% in argon). One can see that the resulting nanowires have a relatively large diameter of 50 nm and an aspect ratio of

Figure 1.3: (a),(d) Scanning electron micrograph of silicon nanowires grown with gold on a <111> oriented silicon substrate. (b),(e) High resolution TEM image of a silicon nanowire grown epitaxially on a <111> oriented silicon substrate. (c) High resolution TEM image of the tip region of a thin silicon nanowire.

about ten. A large percentage of the wires are grown in the [111] direction perpendicular to the substrate surface, which is an indication for epitaxial growth. Due to the extended annealing, the nanowires are quite homogeneous in diameter and well separated from each other. Some of the nanowires exhibit kinks, i.e. abrupt changes in their growth direction. This is an often observed phenomenon [Wag68] that might be related to the low growth pressure [Oza98] or/and the low growth temperature [Wes97a]. The nanowires show only slight tapering, if any, which is typical for silicon nanowires grown at low temperatures with gold as catalyst. Figure 1.3 (b) shows a cross section transmission electron microscope (TEM) image (Jeol 4010) of the region where a thin silicon nanowire is attached to the substrate. Clearly, the epitaxial nature of the transition between the (111)-oriented substrate and the nanowire can be observed. In addition, the single crystalline nature of the silicon nanowire is apparent. This can also be seen in Fig. 1.3(c), where the gold tip and the tip region of a silicon nanowire with 10 nm diameter is shown. Figure 1.3 (d) and (e) show the largest and smallest nanowire we found so far. It is remarkable that the growth process works equally well from 6 nm to about 600 nm, hence over a diameter variation

of about two orders of magnitude. Note also the epitaxial contact to the substrate, and the expansion at the nanowire base, visible in Fig. 1.3(e).

#### **1.5** Using other Catalysts than Gold

Gold is the catalyst most frequently used for nanowire synthesis in general, and silicon nanowire growth in particular. There are some criteria which make gold a well suited catalyst material. The first, and maybe most important one, is related to the low temperature eutectic point of the Au/Si phase diagram (see Fig. I.1). This allows for growth temperatures as low as  $360 \,^{\circ}$ C, which becomes important, if silicon nanowire synthesis is combined with process steps that do not allow high temperatures. Another important aspect of the Au/Si phase diagram is the relatively high silicon solubility at the eutectic temperature. This makes the growth process robust against fluctuations of the silicon concentration, as will readily be shown. Let us consider a half-spherical Au/Si catalyst particle of 10 nm in diameter. At the eutectic point the number of gold atoms in this droplet is approximately  $1.5 \times 10^4$ , compared to about  $2.5 \times 10^3$  silicon atoms. Given the smallest possible fluctuation of plus or minus one silicon atom, the relative concentration change will be only 0.04%. However, suppose the silicon solubility at the eutectic point would be very small, let's say 0.004%, like for an In/Si alloy of eutectic composition. Then a fluctuation of plus or minus one silicon atom would cause a relative concentration change of more than 100%. This might have severe effects on the stability of the growth process.

Another argument for the use of gold as a catalyst is the low vapor pressure at the moderate growth temperatures. A re-evaporation of the catalyst material during growth can practically be neglected. The high chemical stability of gold is an additional advantage, especially in view of a pre-growth processing of the substrate. A patterning of the substrate with a well defined arrangement of gold particles, for example, including subsequent nanowire growth can be easily done [Wes97b].

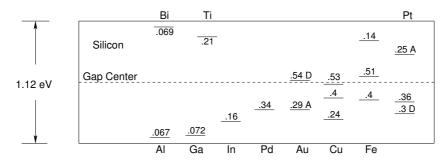

Figure 1.4: Ionization energies of different impurities in silicon, after [Sze81b]

On the other hand, the high chemical stability of gold is one of the most severe drawbacks. A possible gold contamination of equipment used for a post-growth processing of the nanowires can hardly be removed. This alone would not be that severe, if gold would not be known to create very efficient recombination centers in silicon - a feature of special importance for those electronic applications, which rely on a low electron-hole recombination rate. Assuming identical electron and hole cross sections  $\sigma$ , the recombination rate U of a trap is given by

$$U = \sigma \sqrt{3kT/m*} N_t \frac{pn - n_i}{p + n + 2n_i \cosh\left(\frac{E_t - E_i}{kT}\right)} \qquad [Sze81b], \qquad (1.4)$$

where  $N_t$  is the trap density and  $E_t$  is the energy level of the trap. One can see that the recombination rate strongly depends on the energy difference between the trap level  $E_t$  and the band gap middle  $E_i$ , such that deep levels, located close to the band gap middle, cause a maximal recombination rate. As shown in Fig. 1.4, gold does create such deep levels.

Therefore, especially in view of future electronic applications, it is desirable to replace gold with a catalyst material ideally offering all the advantages of gold, but being less problematic with respect to the defects it creates. We tested six different materials - palladium, iron, dysprosium, indium, bismuth, and aluminum. The first three are known to form metal silicides, having melting points beyond the growth temperature that can be applied in our system. Thus growth is presumably catalyzed by a solid catalyst particle. The last three elements - indium, bismuth, and aluminum - are characterized by a eutectic point at low or moderate temperatures, which in principle allows for the vapor-liquid-solid growth of silicon nanowires.

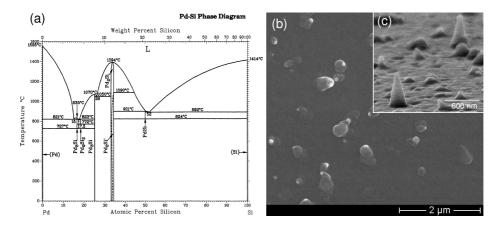

#### 1.5.1 Palladium

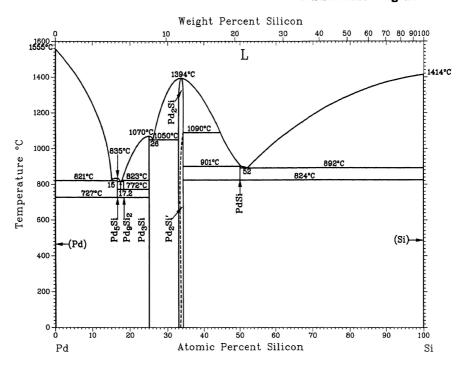

Figure 1.5: (a) Pd/Si phase diagram [Mas90b], see also Fig. A.4. (b) Top view SEM image of growth attempt using Pd as catalyst. Inset: tilted view  $(80^\circ)$  SEM image of nanowires grown with Pd as catalyst.

From the point of view of electronic compatibility, palladium is an interesting catalyst. It only produces one electric defect, 0.34 eV above the conduction band (see Fig. 1.4). The Pd/Si phase diagram in Fig. 1.5(a) shows different palladium silicides for temperatures below 800 °C. The lowest temperature eutectic point is located at about 800 °C, a temperature beyond the possibilities of our equipment. For the growth experiment we in situ deposited

a thin layer of palladium onto a hydrogen-terminated (100)-oriented silicon wafer using an electron beam evaporation source. After transferring the wafer to the growth chamber, the wafer was annealed at  $670 \,^{\circ}$ C for ten minutes to break up the palladium film. Then the growth chamber was flooded with diluted silane (5% in argon, 40 sccm) till a pressure of 2 mbar was reached. This pressure was kept constant for 6 min. Afterwards the silane flow was switched off, and the chamber is evacuated. A top view scanning electron micrograph of the sample is shown in Fig. 1.5(b). One can see that a low density of nanostructures was obtained. Most of them show a small particle at their tip, presumably consisting of palladium silicide. As shown in Fig. 1.5(c), some of these nanostructures are grown vertically with respect to the substrate, and these might be classified as strongly tapered nanowires.

#### 1.5.2 Iron

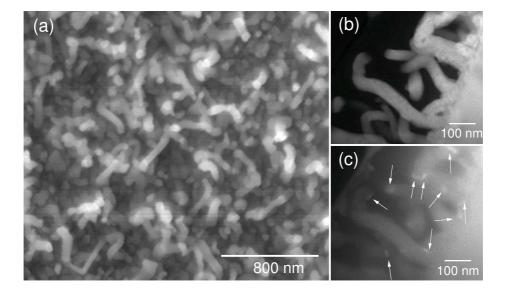

Figure 1.6: (a) Top view scanning electron micrograph of silicon nanowires grown with Fe. (b) TEM cross section image of the silicon nanowires grown with Fe. (c) EFTEM image at the Fe L-edge; white arrows indicate the iron rich particles.

As mentioned before, one element that proved to be able to promote the growth of silicon nanowires, is iron. But either extremely high temperatures (1200 °C) [Mor98], or oxygen-rich conditions [Liu01] had to be applied. Our experiments, on the contrary, were performed at low temperatures and in nominally oxygen-free environment. Iron was deposited in situ as a film of 1 nm thickness onto a hydrogen-terminated silicon wafer, using an electron beam evaporation source. Without an intermediate annealing step, the wafer was heated to 580 °C. After reaching this temperature the chamber was flooded with diluted silane, reaching a pressure of 2.8 mbar after two minutes. Growth was terminated

after six minutes. As shown in Fig. 1.6(a), a large quantity of wire-like structures was produced this way. A preferential growth direction could not be identified. In contrast to the nanowires grown with gold, TEM investigations revealed that the wires exhibit a large number of crystallographic defects. Growth starts with a few layers of defect free silicon. The longer the wire grows, the greater the density of crystallographic defects becomes. Finally, the nanowires are polycrystalline. According to the Fe/Si binary phase diagram, a liquid phase is absent at the growth temperature, and indeed, droplet-like structures at the tip of the wires can neither be seen in Fig. 1.6(a), nor in the cross section transmission electron micrograph (Philips CM20FEG) shown Fig. 1.6(b). However, energy filtered TEM (EFTEM) (Fig. 1.6(c)) at the iron L-edge revealed several iron-containing, plate-shaped particles. Analogously to the growth of silicon nanowires using titanium [Kam01] as catalyst, the particles presumably consist of an iron silicide. In this case, growth cannot be described by the vapor-liquid-solid mechanism, but rather by a vapor-solid-solid mechanism.

#### 1.5.3 Dysprosium

Figure 1.7: (a) Top view scanning electron micrograph of silicon nanowires grown with Dy. (b) TEM cross section image of the silicon nanowires grown with Dy.

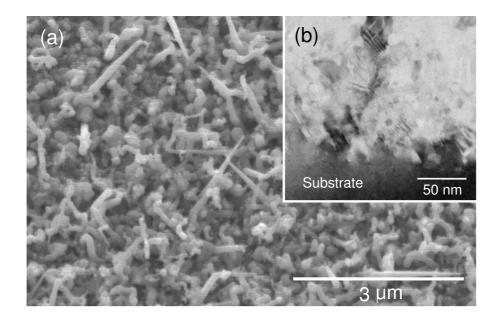

A metal, which to our knowledge has not been reported by other groups as a catalyst for silicon nanowire growth, is dysprosium. In our experiments 0.4 nm of dysprosium were in situ deposited on a hydrogen-terminated silicon wafer. The wafer was subsequently heated to the growth temperature of 630 °C with the silane partial pressure set to 0.15 mbar.

The wires produced in this way are shown in Fig. 1.7(a). Most interesting are the long, tapered, needle-like structures. Their strong tapering might be explained by an additional overgrowth of the wire. In the cross section transmission electron micrograph shown in Fig. 1.7(b) one can see that also the wires grown with dysprosium exhibit a large number of crystallographic defects. Similar to iron, the Dy/Si binary phase diagram shows no liquid phase at the growth temperature. Hence growth, catalyzed by a solid dysprosium silicide particle, offers the most probable explanation.

#### 1.5.4 Bismuth

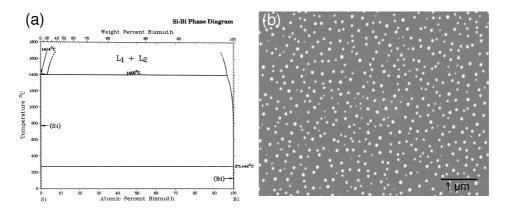

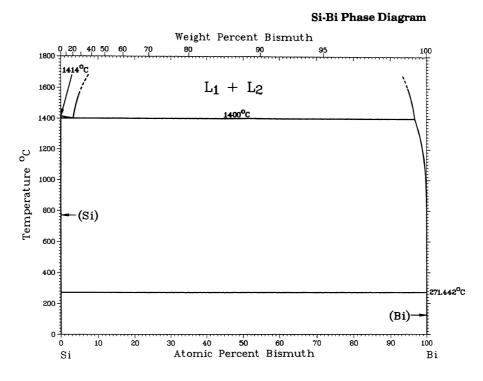

Figure 1.8: (a) Bi-Si phase diagram [Mas90a], see also Fig. A.5. (b) Top view SEM of growth attempt using Bi.

Let us now turn to the catalyst metals that are characterized by a eutectic point in the binary metal/Si phase diagram. Bismuth is an interesting candidate for replacing gold. The electronic level is close to the conduction band, thus bismuth would cause an ndoping of the nanowires. As shown in Fig. 1.8(a), the Bi/Si phase diagram has a eutectic point at 271 °C, which in principle would allow for silicon nanowire growth at very low temperatures. For the growth experiments, about 1 nm of bismuth was in situ deposited onto hydrogen-terminated <111> oriented silicon wafers by an electron beam evaporation source. Different growth conditions were tested with similar outcome. Figure 1.8 (b) shows a typical top view scanning electron micrograph of a sample that was processed at a temperature of  $510 \,^{\circ}$ C and a pressure of 1.9 mbar. A high density of droplets with a size of the order of 100 nm can be observed, but apparently no nanowires are present. One possible reason for the failure of the growth experiments might be the small surface tension,  $\sigma_l$ , of the Bi/Si droplets. According to Nebolsin et al. [Neb03] the surface tension of the liquid  $\sigma_l$  has to be greater than  $\sigma_s/\sqrt{2}$ , with  $\sigma_s$  being the surface tension of solid silicon. This requirement is not met by a Bi/Si alloy. Also the extremely small silicon solubility at 500 °C might be a possible cause for the failure of the experiments.

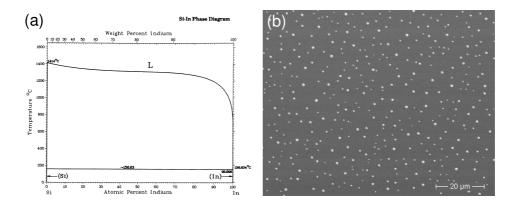

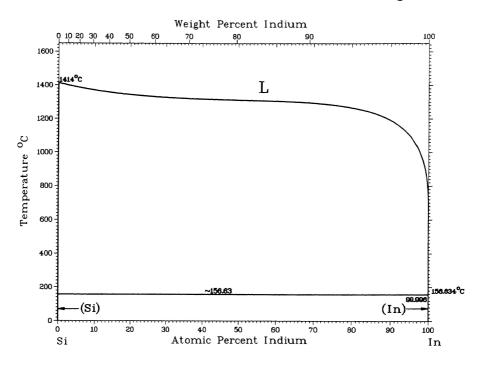

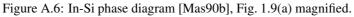

Figure 1.9: (a) In-Si phase diagram [Mas90b], see also Fig. A.6. (b) Top view SEM of growth attempt using In.

#### 1.5.5 Indium

The characteristic of the binary In/Si phase diagram, shown in Fig. 1.9(a), is similar to the Bi/Si phase diagram, as it also exhibits a low temperature eutectic point at  $180 \,^{\circ}\text{C}$  at a very low silicon concentration. But in contrast to bismuth, indium creates an electronic level in silicon that is located 0.16 eV above the valence band edge, thus causing a p-doping of the nanowires. Different growth conditions were tested, yet without success. The result presented in Fig. 1.9(b) was obtained with about 4 nm of indium, deposited onto a hydrogen-terminated (111) silicon wafer. We used a growth temperature of 570 °C and a pressure of 1.8 mbar. Figure 1.9 (b) exhibits a distribution of large droplets, but no silicon nanowires can be found. Like for bismuth, the small indium surface tension might account for the failure of the experiment. As previously discussed, also the low silicon solubility at the growth temperature could have prevented the growth of nanowires.

#### 1.5.6 Aluminum

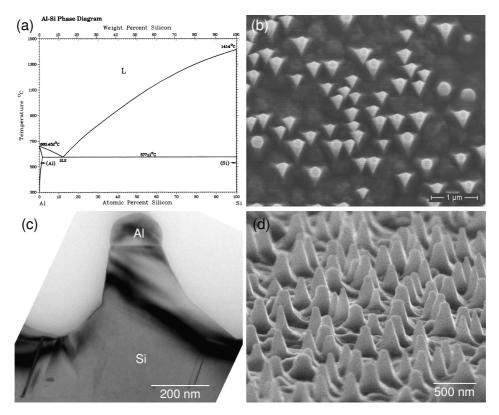

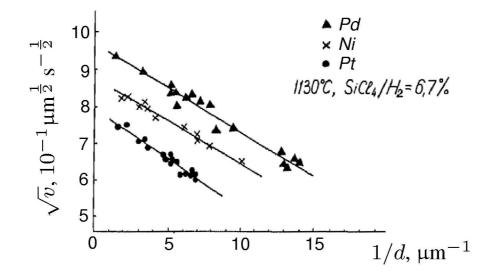

Aluminum is probably the most promising candidate for the replacement of gold as catalyst for silicon nanowire synthesis, as the Al/Si phase diagram (see Fig. 1.10(a)) exhibits the closest similarity to the Au/Si phase diagram. Like this, it is of the simple eutectic type, with a single eutectic point located at a moderate temperature of 577 °C. Also the silicon concentration of 12% is comparable to the silicon concentration of 19% at the Au/Si eutectic point. However, regarding the electronic properties, aluminum offers great advantages compared to gold. Aluminum creates an electronic defect 0.067 eV (see Fig. 1.4) above the valence band edge such that nanowires grown with aluminum would be p-doped. The most important argument in favor of aluminum is that it is compatible with existing electronics fabrication technology.

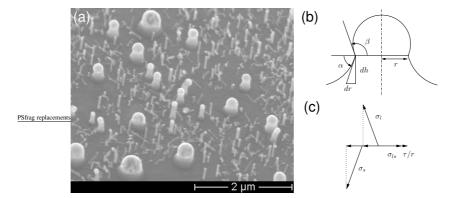

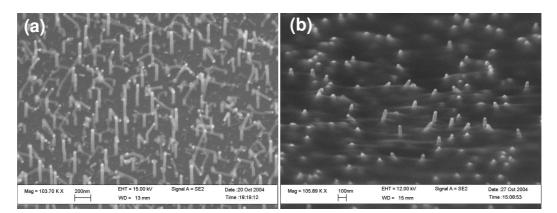

In our experiments we deposited about 1 nm of aluminum, using a thermal evaporation source, in situ onto a hydrogen terminated (111)-oriented silicon wafer. After heating the wafer to a temperature of 510 °C, the silane flow (40sccm 5% in argon) was switched

on. Three minutes later, at a chamber pressure of 4.3 mbar, the wafer temperature was increased to 620 °C. Directly after reaching this temperature, a change of color of the wafer could be observed. Temperature and pressure were kept constant for another 16 minutes. A tilted scanning electron micrograph of the resulting nanowires is displayed in Fig. 1.10(b). The silicon nanowires are strongly tapered and facetted, showing a three-fold symmetry and in addition a particle at their tip. The SEM image shown in Fig. 1.10(d) gives a better impression of the shape of the nanowires. Interesting are the well defined surface planes, which we, however, could not clearly identify yet. The TEM image (Philips CM20) of Fig. 1.10(c), shows a cross section of the sample that was cut with respect to the vertical image axis of Fig. 1.10(b). Therefore the left flank of the nanowire appears at a steeper angle than the right flank. One can see that the nanowires are grown epitaxially on the silicon wafer and that they are single crystalline, exhibiting only few defects. Recent experiments indicate that both the tapering and the diameter of the silicon nanowires grown with the help of aluminum can be strongly reduced by optimizing the growth conditions.

Figure 1.10: (a) Al-Si phase diagram [Mas90a], see also Fig. A.7. (b) Tilted view  $(24^{\circ})$  SEM image of silicon nanowires grown with Al. (c) TEM cross section image of the silicon nanowires grown with Al. (d) Tilted view  $(80^{\circ})$  SEM image of silicon nanowires grown with Al.

#### **1.6 Conclusions of Chapter 1**

To conclude, we have seen that gold is a well suited catalyst for silicon nanowire growth at moderate temperatures. By choosing the proper annealing conditions, both the average diameter and the density of the Au/Si alloy particles can be adjusted. The resulting nanowires are usually single crystalline and grown epitaxially on the substrate. In addition, different metals have been tested with regard to their ability of replacing gold as catalyst for nanowire growth. Palladium, iron, and dysprosium proved to be able to catalyze the growth of silicon nanowires at temperatures around 600 °C. However, the crystalline quality of the nanowires synthesized with the help of iron and dysprosium was rather poor. Silicon nanowire growth with the help of bismuth and indium did not succeed, at least in the parameter range we tried. The most promising alternative to gold seems to be aluminum, with which nanowires of high crystalline quality can be produced at temperatures around the eutectic point of the Al/Si alloy.

### **Chapter 2**

# Diameter Dependence of the Growth Velocity

A possible integration of epitaxially grown silicon nanowires into a complex device architecture necessarily demands a high level of control over the nanowire morphology. One has to be able to control the nanowire length, diameter, and growth direction simultaneously; and ideally independently of each other. However, a well-defined nanowire morphology cannot be achieved without a fundamental understanding of the factors that determine length, diameter, and growth direction of the nanowires. Particular attention has to be payed to possible inter-dependencies between these three parameters, as this of course limits the parameter space.

This chapter and the two chapters following thereupon, each deal with one specific fundamental aspect of the length, the diameter, and the growth direction of silicon nanowires. In Chapter 3 the diameter of epitaxially grown silicon nanowire is considered. Although the diameter is basically constant over almost the entire length, the base of the nanowire, that is the region where the nanowire is attached to the substrate, exhibits a diameter expansion. We will demonstrate that the origin of this expansion is directly related to the vapor-liquidsolid (VLS) mechanism, and that the equilibrium mechanics of the liquid catalyst droplet in the initial stage of growth accounts for the shape of this expansion. Chapter 4 deals with the diameter dependence of the crystallographic growth direction. We present experimental results proving that the crystallographic growth direction of epitaxially grown silicon nanowires is diameter-dependent and propose a model for this diameter dependence.

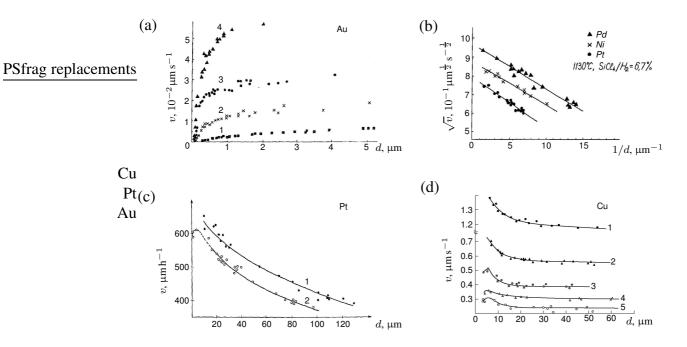

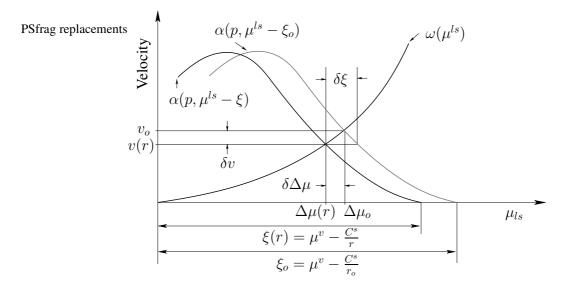

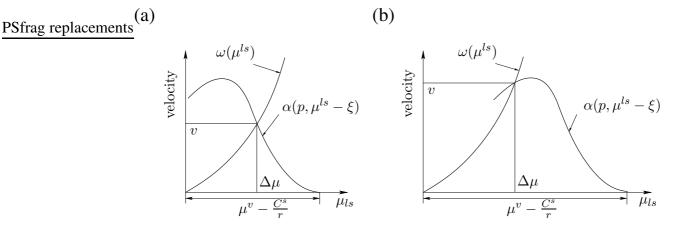

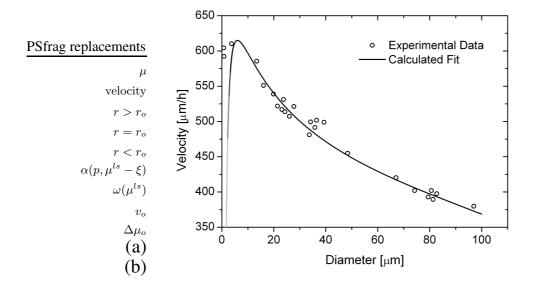

In this chapter we focus on the nanowire length, or - more accurately speaking - on the main factor that determines the nanowire length - the growth velocity. The nanowire growth velocity is known to be diameter-dependent, a phenomenon related to the Gibbs-Thomson effect. However, we will see in the course of this chapter that the influence of the Gibbs-Thomson effect on the growth velocity is more subtle than usually expected, as the diameter dependence of the growth velocity is strongly affected by the applied growth conditions.

#### 2.1 Introduction

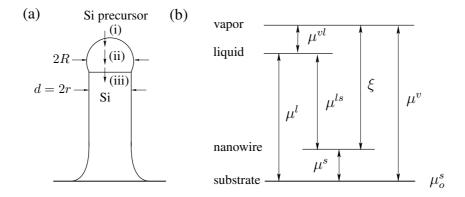

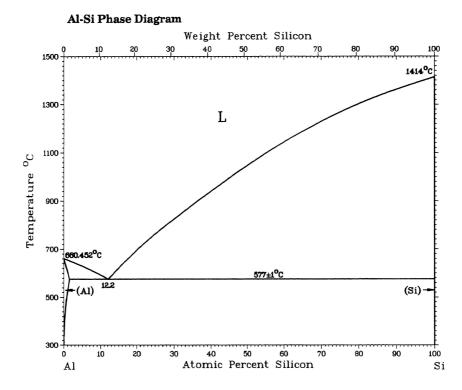

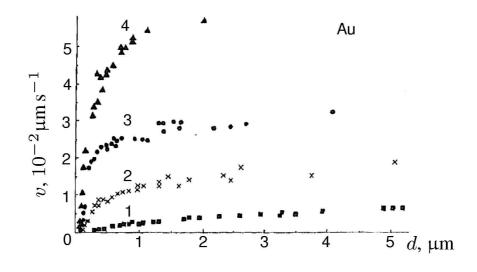

A schematic of the vapor-liquid-solid (VLS) growth mechanism, the most widely used approach for the synthesis of silicon nanowires, is shown in Fig. 2.1(a). The essential ingredient for this technique is a liquid metal/silicon alloy droplet that enables the growth of rod-like structures. The necessary silicon for the nanowire growth is usually supplied by a gaseous silicon precursor like silane, SiH<sub>4</sub>, or silicon tetrachloride, SiCl<sub>4</sub>. Due to the larger sticking coefficient of the droplet, compared to the bare silicon surface, unidirectional growth is favored. At the droplet surface, the silane molecules are cracked, and the resulting silicon atoms are incorporated in the droplet. There they diffuse through the droplet to the liquid-solid interface at the bottom of the droplet, where they form the silicon nanowire. Thus, the vapor-liquid-solid mechanism of silicon nanowire growth basically consists of three steps, see Fig. 2.1(a). First, the adsorption and cracking of the Si precursor at the surface of a liquid metal/Si alloy droplet (i); the thereby produced Si is incorporated in the droplet at a rate  $\rho_{inc}$  [mol/unit time]. Second, the diffusion of Si through the droplet (ii). And third, the crystallization of the Si nanowire at the liquid-solid interface (iii), proceeding at a rate  $\rho_{cry}$  [mol/unit time].

Especially in the 1970s several authors [Giv75, Boo71, Wey78] discussed, which of these three steps is rate-determining for the VLS growth, and just recently this topic was brought up again [Kod06]. Only the diffusion step can be excluded with a high probability, since for droplets of microscopic dimensions, diffusion through the liquid alloy is too fast as to be rate determining. Bootsma and Gassen [Boo71], mainly in view of the pressure dependence of the growth velocity, favored step one, the incorporation step. In contrast to this, Givargizov [Giv87b] took the opinion that the crystallization of the nanowire at the liquid-silicon interface is rate determining. His main argument was that the growth velocity depends on the crystallographic growth direction, which, from his point of view, could only be explained if step number three is taken to be the rate determining one.

Yet, this discussion, whether  $\rho_{inc}$  or  $\rho_{cry}$  is rate determining, does not account for the full complexity of the problem. First of all, the influence of the growth parameters, e.g. silane pressure or temperature, on the rate balance is not considered. One cannot exclude a priori that for one parameter range one step is rate determining, whereas for another parameter range, the other. Furthermore, both rates are implicitly dealt as independent processes - an assumption, which is most likely unjustified, as both  $\rho_{inc}$ , and  $\rho_{cry}$  probably depend on the silicon chemical potential of the liquid droplet. In this case, both processes could interact with each other via this chemical potential. In a steady state situation, where  $\rho_{inc}$  equals  $\rho_{cry}$ , the silicon chemical potential of the droplet needs to adjust in a way that both rates level out. As a consequence of this, we are generally facing a situation where the interplay of both rates determines the growth velocity instead of one rate.

Figure 2.1: (a) Schematic of the VLS mechanism: (i) incorporation, (ii) diffusion, (iii) crystallization. (b) Chemical potentials (CPs):  $\mu_o^s = CP$  of the Si substrate,  $\mu^v = CP$  of the Si vapor,  $\mu^s = CP$  of the Si nanowire,  $\mu^{vl} = CP$  difference between the Si vapor and the liquid droplet,  $\mu^{ls} = CP$  difference between the Si nanowire,  $\xi = CP$  difference between the Si vapor and the Si nanowire.

#### 2.2 Definitions and Experimental Results

We only consider the silicon chemical potentials. As a referce point we choose the chemical potential of the substrate  $\mu_o^s$ , which is fixed by the boundary conditions. Also fixed by the boundary conditions is the chemical potential of the vapor  $\mu^v$ . Due to the surface contribution to the Gibbs free energy, the chemical potential of a nanowire of radius r is increased by an amount proportional to the surface to volume ratio, to the specific surface energy of the nanowire,  $\sigma^s \approx 1.24 \,\mathrm{J \,m^{-2}}$  [Jac63], and to the molar volume of solid silicon,  $\Omega^s \approx 12 \,\mathrm{cm^3/mol}$ . This is the so-called Gibbs-Thomson effect, sometimes also referred to as Laplace-Young effect. Thus, the chemical potential of a silicon nanowire  $\mu^s$  with respect to the silicon substrate can be expressed as

$$\mu^s = \frac{C^s}{r} \qquad [\text{Def66, Tan04}], \tag{2.1}$$

with  $C^s$  defined as  $C^s = 2\Omega^s \sigma^s$ . A similar relation holds for  $\mu^l$ , the chemical potential of the liquid metal/silicon droplet

$$\mu^l = \mu_o^l + \frac{C^l}{R} \,. \tag{2.2}$$

Here, R is the droplet radius and  $\mu_o^l$  is the chemical potential of a droplet of infinite size. The constant  $C^l = 2\Omega^l \sigma^l$ , with  $\sigma^l$  and  $\Omega^l$  being the surface tension and the molar volume of the liquid alloy. As shown in Fig. 2.1,  $\mu^{vl}$  and  $\mu^{ls}$  are the chemical potential differences between the vapor and the liquid droplet, and between the liquid droplet and the silicon nanowire, respectively. The quantity  $\xi$  is defined as the chemical potential difference between vapor and silicon nanowire. According to their definitions, these three quantities have to fulfill the following relation

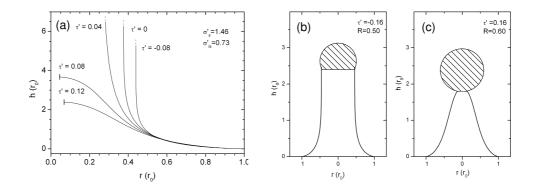

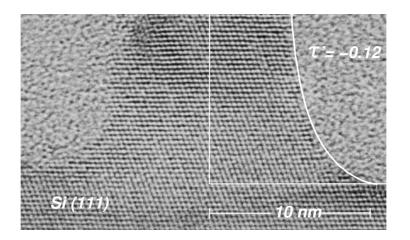

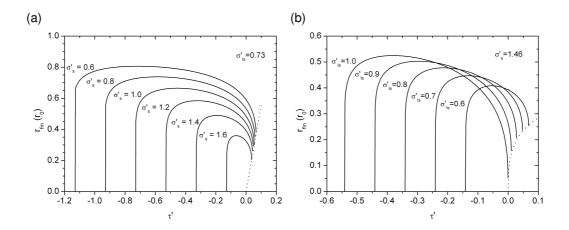

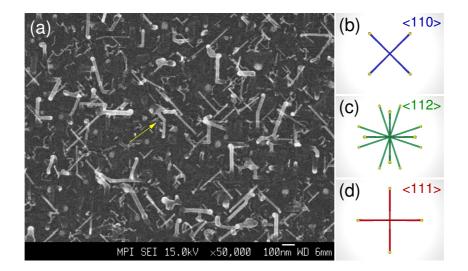

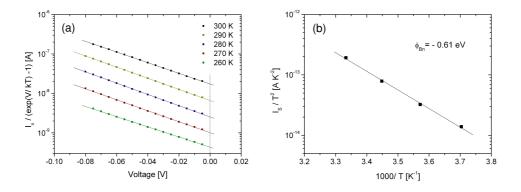

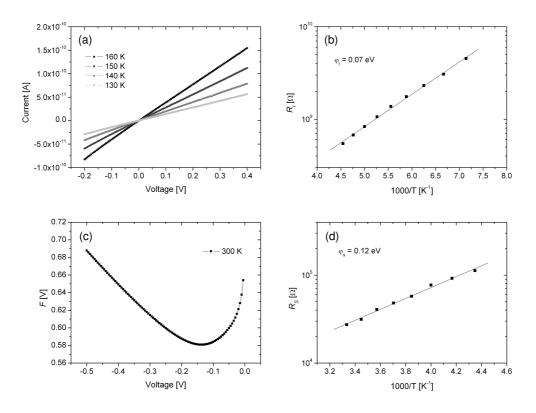

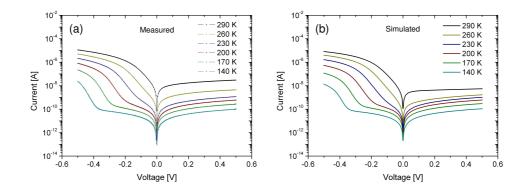

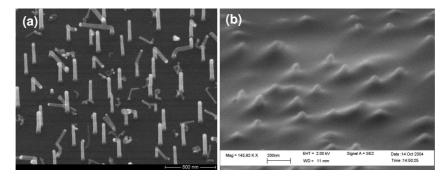

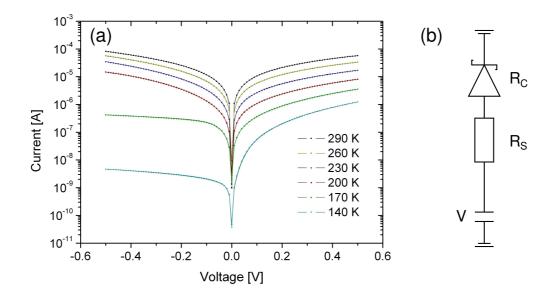

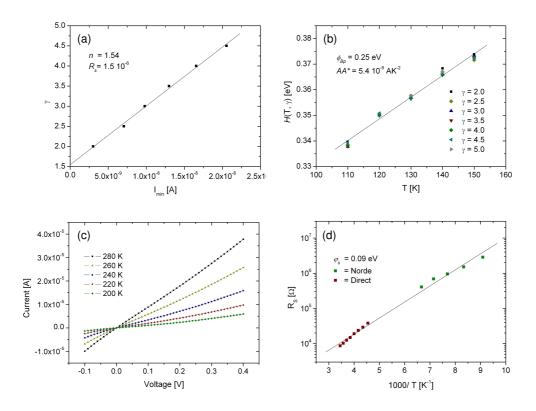

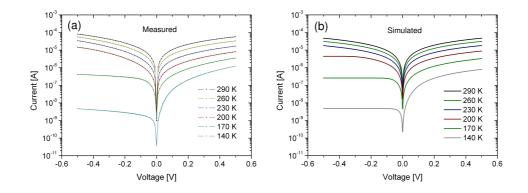

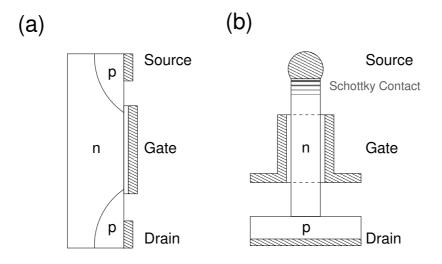

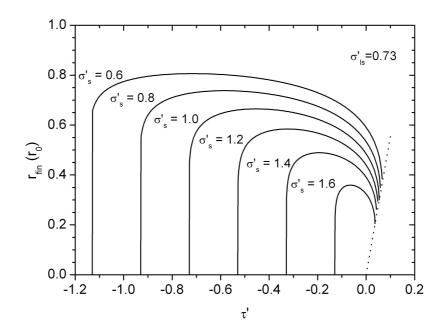

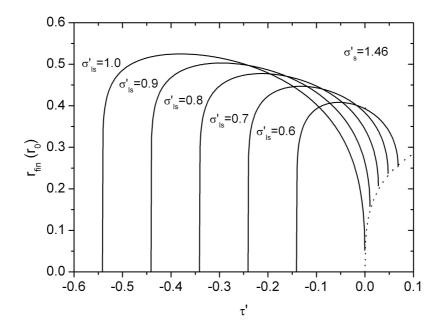

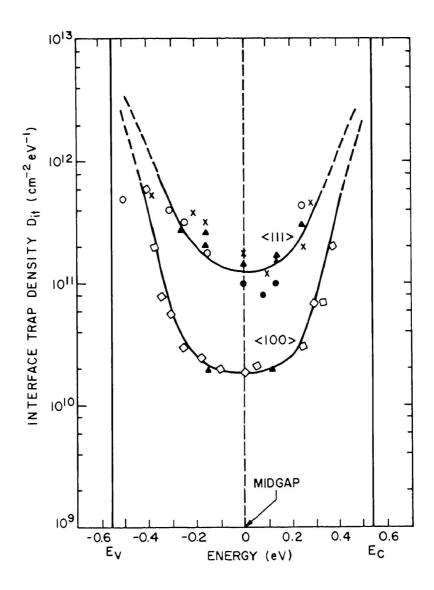

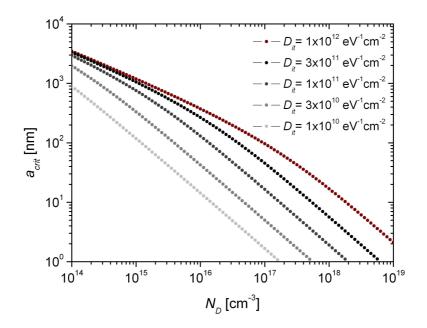

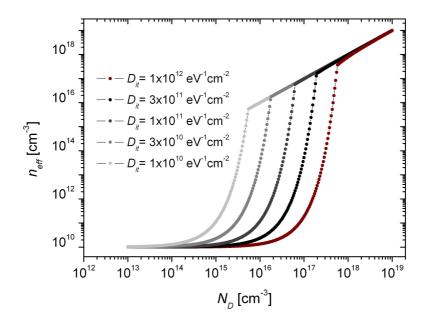

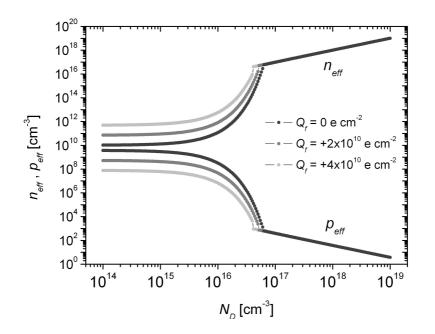

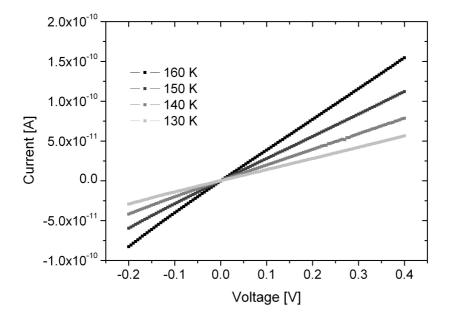

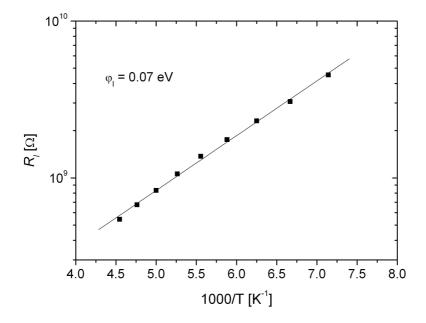

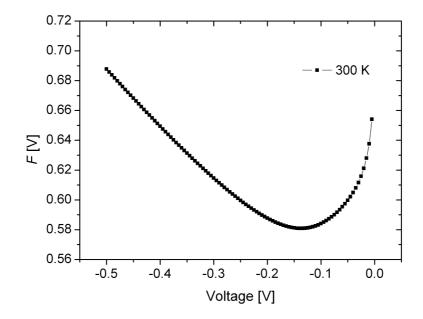

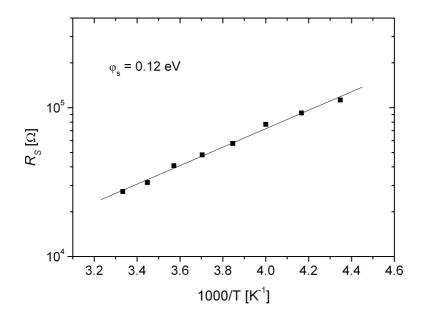

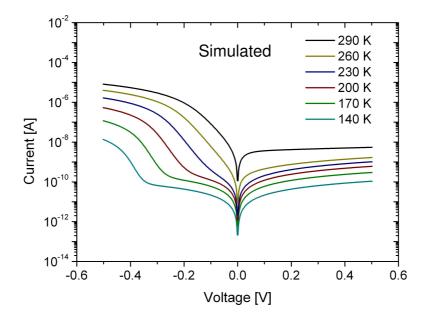

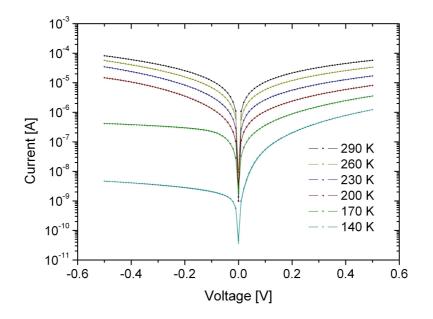

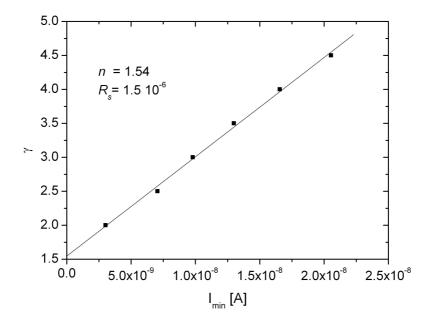

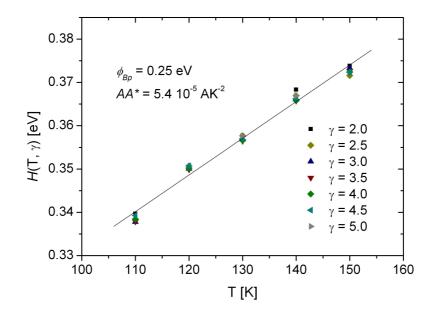

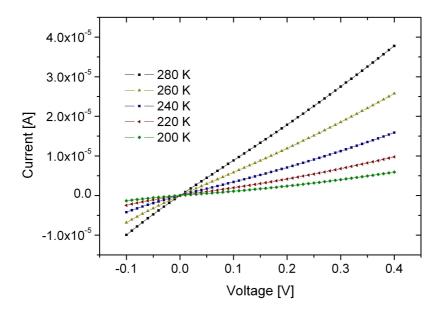

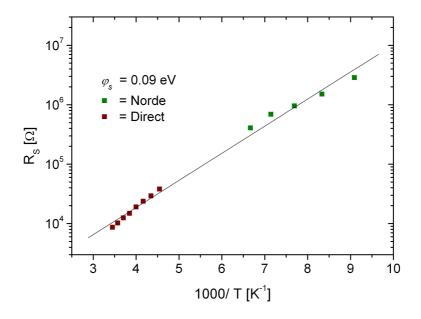

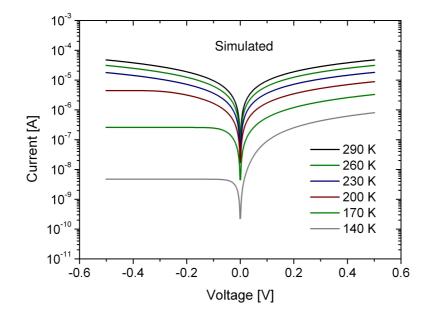

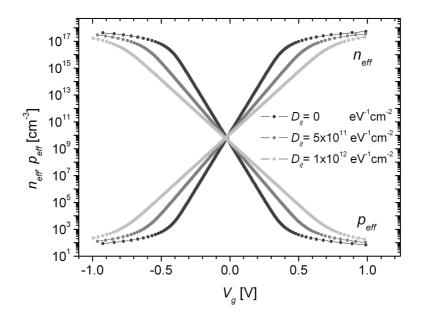

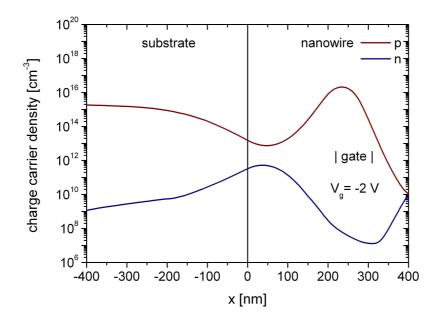

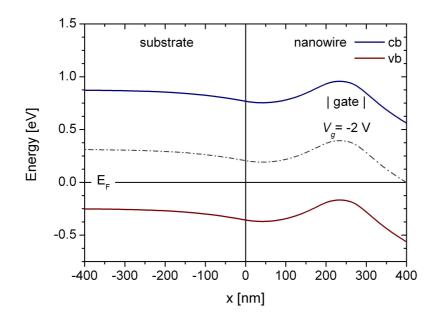

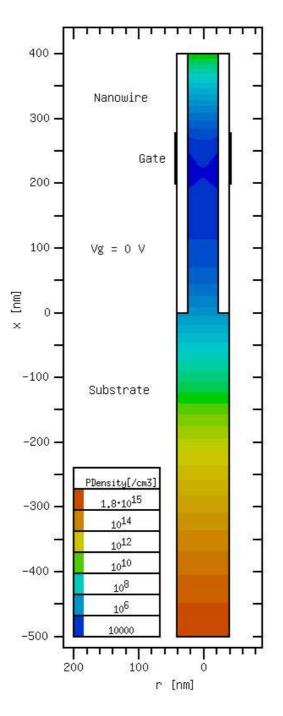

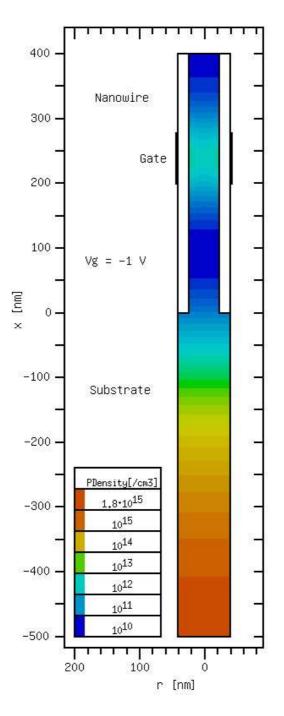

$$\xi = \mu^{vl} + \mu^{ls} \,. \tag{2.3}$$